SI9241ADY-T1-E3 下降沿觸發的JK觸發器初始狀態

發布時間:2020/1/17 12:41:21 訪問次數:1984

SI9241ADY-T1-E3描述它有兩個輸入(D和E)(1個輸出(Q)。對于鎖存器來說,當輸入控制信號處于有效電平時(即E=1時),其輸出Q跟隨輸入信號D的變化;當控制信號無效時,輸出Q保持不變。所以在anways語句中@符號之后的“事件控制表達式”使用了電平敏感事件,說明如果輸人信號E或者D發生變化,就會執行一次后面的if語句,但只有E為邏輯1時,輸入D的變化才能傳送到輸出Q;否則,輸出Q將保持不變。注意,由于輸出Q是在過程語句中被賦值,所以必須將它聲明為reg類型的變量。

例5,5.1

//Description of D 1atch(See Fig. 5.2.10a or Fig. 5.2.11a)

nlodule D~latch(Q,D,E);

output Q;

input D, E;

reg Q;

always@(E or D)

iF(E)Q (= D;

endInodule

例5.5.2中描述了三種上升沿觸發的D觸發器。第一個模塊描述的是功能如圖5.3.2或圖5.3,5那樣的基本D觸發器,其輸出信號為Q,輸人信號為D和CP。由于是在過程語句中被賦值,輸出信號Q必須聲明為reg型變量。在a1ways語句@符號之后的“事件控制表達式”中使用了邊沿觸發事件,即posedge CP,使其后的語句Q(=D僅在CP上升沿期間將D的值賦給Q,而在其他任何時間,無論D信號如何變化,都不能改變Q的狀態。

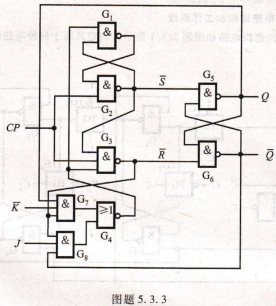

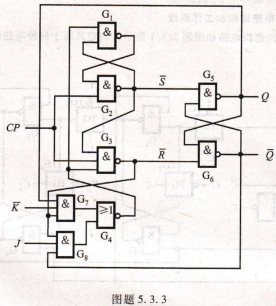

例5.5,2中第二個模塊描述了如圖5.3.3或圖5.3.6所示具有異步直接置1、置0功能的D觸發器。在always語句的“事件控制表達式”中,比前一模塊增加了兩個異步觸發事件negedge sd和negedge Rd。在這種表達式中,可以有一個或多個異步事件,但必須有一個事件是時鐘事件,它們之間用關鍵詞or進行連接。這個模塊中的觸發事件表示,在輸入信號CP的上升沿到來時,或sd或Rd跳變為低電平時,后面的if-e1se語句就會被執行一次。

negedge sd和negedge Rd是兩個異步事件,它與if(sd‖Rd)語句相匹配。如果條件具備,接下來,如果sd為邏輯0(if(sd)),則將輸出Q置1,QN置0;否則(else)將輸出Q置0,QN置1;如果sd和Rd均不為0,只能是時鐘CP上升沿到來,則將輸人D傳送到輸出Q, D傳送到QN。從語句執行的順序可以看出,如果直接置1或置0事件和時鐘事仵同時發生,則置1或置0事件有更高的優先級別,這與圖5.3.3或圖5,3.6中電路的功能是一致的。

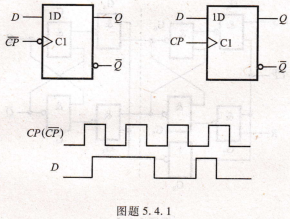

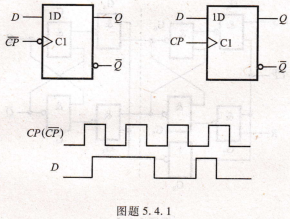

上升沿觸發和下降沿觸發的D觸發器邏輯符號及時鐘信號CP(CP)和D的波形如圖題5,4.1所示。分別畫出它們的Q端波形。設觸發器的初始狀態為0。

邏輯電路如圖題5.4,4所示,5.4.5 電路如圖題5.4.5所示,設波形,試畫出在CP作用下,φ。、φ1、φ2,各觸發器的初態為0,畫出在CP脈D試用卡諾圖化簡表5.4.2表達的邏輯關系,并將結果與式(5.4.2)核對。

設下降沿觸發的JK觸發器初始狀態為0,CP、J、K信號如圖題5.4.3所示,

試畫出觸發器Q端的,輸出波形和φ3的波形沖作用下Q端.

SI9241ADY-T1-E3描述它有兩個輸入(D和E)(1個輸出(Q)。對于鎖存器來說,當輸入控制信號處于有效電平時(即E=1時),其輸出Q跟隨輸入信號D的變化;當控制信號無效時,輸出Q保持不變。所以在anways語句中@符號之后的“事件控制表達式”使用了電平敏感事件,說明如果輸人信號E或者D發生變化,就會執行一次后面的if語句,但只有E為邏輯1時,輸入D的變化才能傳送到輸出Q;否則,輸出Q將保持不變。注意,由于輸出Q是在過程語句中被賦值,所以必須將它聲明為reg類型的變量。

例5,5.1

//Description of D 1atch(See Fig. 5.2.10a or Fig. 5.2.11a)

nlodule D~latch(Q,D,E);

output Q;

input D, E;

reg Q;

always@(E or D)

iF(E)Q (= D;

endInodule

例5.5.2中描述了三種上升沿觸發的D觸發器。第一個模塊描述的是功能如圖5.3.2或圖5.3,5那樣的基本D觸發器,其輸出信號為Q,輸人信號為D和CP。由于是在過程語句中被賦值,輸出信號Q必須聲明為reg型變量。在a1ways語句@符號之后的“事件控制表達式”中使用了邊沿觸發事件,即posedge CP,使其后的語句Q(=D僅在CP上升沿期間將D的值賦給Q,而在其他任何時間,無論D信號如何變化,都不能改變Q的狀態。

例5.5,2中第二個模塊描述了如圖5.3.3或圖5.3.6所示具有異步直接置1、置0功能的D觸發器。在always語句的“事件控制表達式”中,比前一模塊增加了兩個異步觸發事件negedge sd和negedge Rd。在這種表達式中,可以有一個或多個異步事件,但必須有一個事件是時鐘事件,它們之間用關鍵詞or進行連接。這個模塊中的觸發事件表示,在輸入信號CP的上升沿到來時,或sd或Rd跳變為低電平時,后面的if-e1se語句就會被執行一次。

negedge sd和negedge Rd是兩個異步事件,它與if(sd‖Rd)語句相匹配。如果條件具備,接下來,如果sd為邏輯0(if(sd)),則將輸出Q置1,QN置0;否則(else)將輸出Q置0,QN置1;如果sd和Rd均不為0,只能是時鐘CP上升沿到來,則將輸人D傳送到輸出Q, D傳送到QN。從語句執行的順序可以看出,如果直接置1或置0事件和時鐘事仵同時發生,則置1或置0事件有更高的優先級別,這與圖5.3.3或圖5,3.6中電路的功能是一致的。

上升沿觸發和下降沿觸發的D觸發器邏輯符號及時鐘信號CP(CP)和D的波形如圖題5,4.1所示。分別畫出它們的Q端波形。設觸發器的初始狀態為0。

邏輯電路如圖題5.4,4所示,5.4.5 電路如圖題5.4.5所示,設波形,試畫出在CP作用下,φ。、φ1、φ2,各觸發器的初態為0,畫出在CP脈D試用卡諾圖化簡表5.4.2表達的邏輯關系,并將結果與式(5.4.2)核對。

設下降沿觸發的JK觸發器初始狀態為0,CP、J、K信號如圖題5.4.3所示,

試畫出觸發器Q端的,輸出波形和φ3的波形沖作用下Q端.

公網安備44030402000607

公網安備44030402000607