WLAVA30042 X型、Y型和Z型高密度連接接線塊

發布時間:2020/1/22 16:18:39 訪問次數:2057

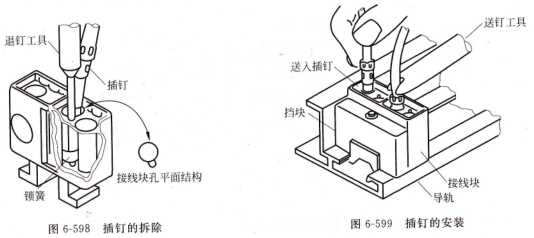

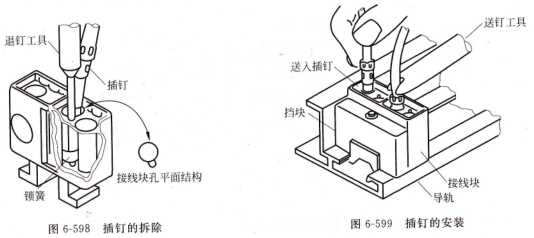

WLAVA30042退釘工按線塊孔平面結構,插釘的拆除,M39029/11-145高密度連接釘用于,BACM15C類型中的X型、Y型和Z型高密度連接接線塊,如圖6-600所示。

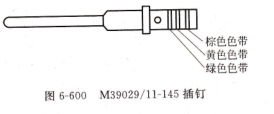

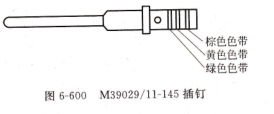

接線塊的安裝,接線塊安裝所需的組件,如圖6-601所示;接線塊在導軌上的安裝方法和安裝位置,如圖6-602和圖6-603所示。

塞塊接線塊相關組件,接線塊在導軌上的安裝,送人插釘擋塊導軌,插釘的安裝,M39029/11-1過5插釘,標準線路施工,送釘E具棕色色帶,綠色色帶導軌上心.

信號進行描述,在硬件電路的行為描述中,有時為了仿真的需要,也用inmal語句給寄存器變量賦初值。inmal語句主要是一條面向仿真的過程語句,不能用于邏輯綜合,因而本書將不作詳細介紹。

always本身是一個無限循環語句,即不停地循環執行其內部的過程語句,直到仿真過程結束。但用它來描述硬件電路的邏輯功能時,通常在always后面緊跟著循環的控制條件,所以always語句的一般用法如下:

always@(事件控制表達式)

begin

塊內局部變量的定義;

過程賦值語句;

end

這里,“事件控制表達式”也稱為敏感事件表,即等待確定的事件發生或某一特定的條件變為“真”,它是執行后面過程賦值語句的條件。“過程賦值語句”左邊的變量必須被定義成寄存器數據類型,右邊變量可以是任意數據類型。be-gin和end將多條過程賦值語句包圍起來,組成一個順序語句塊,塊內的語句按照排列順序依次執行,最后一條語句執行完后,執行掛起,然后anways語句處于等待狀態,等待下一個事件的發生。注意,當begin和end之間只有一條語句,且沒有定義局部變量時,則關鍵詞begin和end可以被省略。

在Verilog中,將邏輯電路中的敏感事件分為兩種類型:電平敏感事件和邊沿觸發事件。在組合電路中,輸入信號的變化直接會導致輸出信號的變化;

時序電路中的鎖存器輸出在使能信號為高電平時亦隨輸人電平而變化,波形如圖5.3.1(a)所示。這種對輸入信號電平變化的響應稱為電平敏感事件。

例如,例4.5.9中的語句

always@ (se1 0r a or b)

說明sel、a或b中任意一個信號的電平發生變化(即有電平敏感事件發生),后面的過程賦值語句將會執行一次。

而觸發器狀態的變化僅僅發生在時鐘脈沖的上升沿或下降沿,如圖5.3.1(b)、(c)所示波形。Ⅴerilog中分別用關鍵詞posedge(上升沿)和negedge(下降沿)進行說明,這就是邊沿敏感事件。例如,語句always@(posedge CP or negedge CR)

說明在時鐘信號CP的上升沿到來或在清零信號CR跳變為低電平時,后面的

過程語句就會執行。

在always語句內部的過程賦值語句有兩種類型:阻塞型賦值語句①和非系Blocking Assignment statement的譯稱。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

WLAVA30042退釘工按線塊孔平面結構,插釘的拆除,M39029/11-145高密度連接釘用于,BACM15C類型中的X型、Y型和Z型高密度連接接線塊,如圖6-600所示。

接線塊的安裝,接線塊安裝所需的組件,如圖6-601所示;接線塊在導軌上的安裝方法和安裝位置,如圖6-602和圖6-603所示。

塞塊接線塊相關組件,接線塊在導軌上的安裝,送人插釘擋塊導軌,插釘的安裝,M39029/11-1過5插釘,標準線路施工,送釘E具棕色色帶,綠色色帶導軌上心.

信號進行描述,在硬件電路的行為描述中,有時為了仿真的需要,也用inmal語句給寄存器變量賦初值。inmal語句主要是一條面向仿真的過程語句,不能用于邏輯綜合,因而本書將不作詳細介紹。

always本身是一個無限循環語句,即不停地循環執行其內部的過程語句,直到仿真過程結束。但用它來描述硬件電路的邏輯功能時,通常在always后面緊跟著循環的控制條件,所以always語句的一般用法如下:

always@(事件控制表達式)

begin

塊內局部變量的定義;

過程賦值語句;

end

這里,“事件控制表達式”也稱為敏感事件表,即等待確定的事件發生或某一特定的條件變為“真”,它是執行后面過程賦值語句的條件。“過程賦值語句”左邊的變量必須被定義成寄存器數據類型,右邊變量可以是任意數據類型。be-gin和end將多條過程賦值語句包圍起來,組成一個順序語句塊,塊內的語句按照排列順序依次執行,最后一條語句執行完后,執行掛起,然后anways語句處于等待狀態,等待下一個事件的發生。注意,當begin和end之間只有一條語句,且沒有定義局部變量時,則關鍵詞begin和end可以被省略。

在Verilog中,將邏輯電路中的敏感事件分為兩種類型:電平敏感事件和邊沿觸發事件。在組合電路中,輸入信號的變化直接會導致輸出信號的變化;

時序電路中的鎖存器輸出在使能信號為高電平時亦隨輸人電平而變化,波形如圖5.3.1(a)所示。這種對輸入信號電平變化的響應稱為電平敏感事件。

例如,例4.5.9中的語句

always@ (se1 0r a or b)

說明sel、a或b中任意一個信號的電平發生變化(即有電平敏感事件發生),后面的過程賦值語句將會執行一次。

而觸發器狀態的變化僅僅發生在時鐘脈沖的上升沿或下降沿,如圖5.3.1(b)、(c)所示波形。Ⅴerilog中分別用關鍵詞posedge(上升沿)和negedge(下降沿)進行說明,這就是邊沿敏感事件。例如,語句always@(posedge CP or negedge CR)

說明在時鐘信號CP的上升沿到來或在清零信號CR跳變為低電平時,后面的

過程語句就會執行。

在always語句內部的過程賦值語句有兩種類型:阻塞型賦值語句①和非系Blocking Assignment statement的譯稱。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

公網安備44030402000607

公網安備44030402000607