RN14WS38.3KF 隨機存取存儲器的共同之處

發布時間:2020/2/10 22:40:34 訪問次數:1363

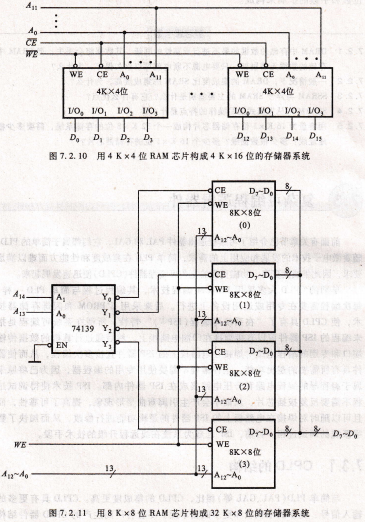

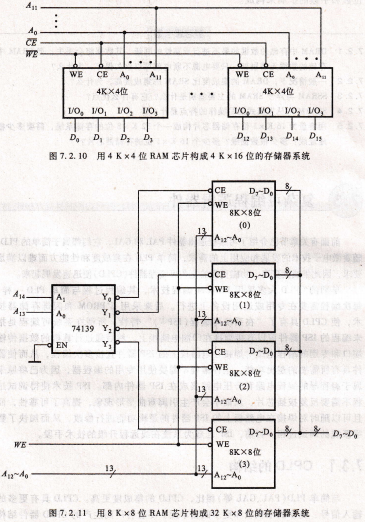

RN14WS38.3KF用4K×4位RAM芯片構成4K×16位的存儲器系統

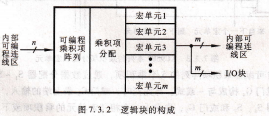

圖7,2,11 用8K×8位RAM芯片構成32K×8位的存儲器系統

實際應用中,常將兩種方法相互結合,以達到字和位均擴展的要求。可見,無論需要多大容量的存儲器系統,均可利用容量有限的存儲器芯片,通過隨機存取存儲器千差萬別,但它們仍有共同之處,圖7.3.1所示是一般CPLD器件的結構框圖。其中邏輯塊①就相當于一個GAL器件(見6,7節),CPLD中有多個邏輯塊,這些邏輯塊之間可以使用可編程內部連線實現相互連接。為了增強對I/0的控制能力,提高引腳的適應性,CPLD中還增加了I/o控制塊。每個I/0塊中有若干個I/o單元。

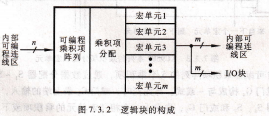

邏輯塊的構成如圖7.3.2所示.它主要由可編程乘積項陣列(即與陣列)、乘積項分配 、宏單元三部分組成 ,其結構類似于GAL.對于不同廠商不同型號的CPLD,邏輯塊中乘積項的輸人變量個數刀和宏單元個數而不完全相同。例如,Xilinx公司的XC9500系列中,乘積項輸人變量有36個 ,宏單元為18個.Altera公司的MAX7000系列有36個乘積項輸人變量,16個宏單元。

各公司CPLD中的邏輯塊名稱不一。如Function Block,FB(Xilinx),Logic Anay Block,LAB(Altera), Genenc Logic Block, GLB(Lattice)。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

RN14WS38.3KF用4K×4位RAM芯片構成4K×16位的存儲器系統

圖7,2,11 用8K×8位RAM芯片構成32K×8位的存儲器系統

實際應用中,常將兩種方法相互結合,以達到字和位均擴展的要求。可見,無論需要多大容量的存儲器系統,均可利用容量有限的存儲器芯片,通過隨機存取存儲器千差萬別,但它們仍有共同之處,圖7.3.1所示是一般CPLD器件的結構框圖。其中邏輯塊①就相當于一個GAL器件(見6,7節),CPLD中有多個邏輯塊,這些邏輯塊之間可以使用可編程內部連線實現相互連接。為了增強對I/0的控制能力,提高引腳的適應性,CPLD中還增加了I/o控制塊。每個I/0塊中有若干個I/o單元。

邏輯塊的構成如圖7.3.2所示.它主要由可編程乘積項陣列(即與陣列)、乘積項分配 、宏單元三部分組成 ,其結構類似于GAL.對于不同廠商不同型號的CPLD,邏輯塊中乘積項的輸人變量個數刀和宏單元個數而不完全相同。例如,Xilinx公司的XC9500系列中,乘積項輸人變量有36個 ,宏單元為18個.Altera公司的MAX7000系列有36個乘積項輸人變量,16個宏單元。

各公司CPLD中的邏輯塊名稱不一。如Function Block,FB(Xilinx),Logic Anay Block,LAB(Altera), Genenc Logic Block, GLB(Lattice)。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

公網安備44030402000607

公網安備44030402000607