UDN2955W 乘積項分配和宏單元

發布時間:2020/2/11 13:11:19 訪問次數:999

UDN2955W可編程乘積項陣列,乘積項陣列有汜個輸入,可以產生而變量的乘積項。一般一個宏單元對應5個乘積項,這樣,在邏輯塊中共有5×屁個乘積項。例如,XC9500系列的邏輯塊中有90個36變量乘積項,MAX7000系列的邏輯塊中有80個36變量乘積項。

乘積項分配和宏單元,不同型號的CPLD器件,乘積項分配和宏單元電路結構也不完全相同,但所要實現的功能大體相似。圖7.3.3所示為XC9500系列的乘積項分配和宏單元電路。圖中S1~S為可編程數據分配器,M1~M5為可編程數據選擇器。為簡明起見,沒有畫出它們的可編程選擇輸入端。

到上一個宏單元來自上一個宏單元,全局置位局復位乘積項配電路,全局時鐘部程區內編線,到可連項輸出使能要單元,來自下一個宏單元 到下一個宏單元.

圖7.3.3 XC9500系列的乘積項分配和宏單元

來自可編程乘積項陣列的5個乘積項,通過數據分配器S1~S5送至宏單元的主或門G4構成與一或式。與此同時,或門G4最上端的輸人,可以通過數據分配器S6、S7和或門G3,取自上一個相鄰宏單元的乘積項或下一個相鄰宏單元的乘積項,從而擴展了乘積項的個數。

宏單元中任何沒有用到的乘積項,都可以經過或門Gl與經S6和S7來自相鄰宏單元的乘積項由或門G2組合在一起,再經過數據分配器S:送到上一個存儲器、復雜可編程器件和現場可編程門陣列.

選擇其來源其中,全局輸出使能控制信號有多個,不同型號的器件,其數量也不同(XC9500系列中r=4,MAX7000系列中r=6。當oE為低電平時,I/0引腳可用作輸入,引腳上的輸入信號經過輸入緩沖器送至內部可編程連線區。到其他I/o單元

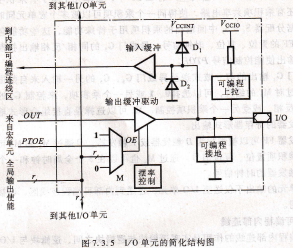

輸入緩沖單元,圖7.3.5 I/o單元的簡化結構圖

圖7.3.5中D1和D2是鉗位二極管,用于I/0引腳的保護。另外,通過編程可以使I/o引腳接上拉電阻或接地,也可以控制輸出擺率(轉換速率SR),選擇快速方式可適應頻率較高的信號輸出,選擇慢速方式則可減小功耗和降低噪聲。ycclNT是器件內部邏輯電路的工作電壓(也稱為核心工作電壓①),而ycc的引入,可以使I/0引腳兼容多種電源系統。

CPLD編程簡介,通過上一節的介紹可以看出,CPLD的各種邏輯功能的實現,都是由其內部的可編程單元控制的。這些單元大多采用E2PROM或閃爍存儲器編程技術。

編程過程就是將編程數據寫入這些單元的過程。這一過程也稱為下載(Down~load)或酉己置(Configure)。

寫人CPLD中的編程數據都是由可編程器件的開發軟件自動生成的。用戶在開發軟仵中輸人設計及要求。利用開發軟件對設計進行檢查、分析和優化,系Core Vdtage的譯稱。到內部可編程連線區,來自宏單元全局輸出使能到其他I/o,存儲器、復雜可編程器件和現場可編程陣列.

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

UDN2955W可編程乘積項陣列,乘積項陣列有汜個輸入,可以產生而變量的乘積項。一般一個宏單元對應5個乘積項,這樣,在邏輯塊中共有5×屁個乘積項。例如,XC9500系列的邏輯塊中有90個36變量乘積項,MAX7000系列的邏輯塊中有80個36變量乘積項。

乘積項分配和宏單元,不同型號的CPLD器件,乘積項分配和宏單元電路結構也不完全相同,但所要實現的功能大體相似。圖7.3.3所示為XC9500系列的乘積項分配和宏單元電路。圖中S1~S為可編程數據分配器,M1~M5為可編程數據選擇器。為簡明起見,沒有畫出它們的可編程選擇輸入端。

到上一個宏單元來自上一個宏單元,全局置位局復位乘積項配電路,全局時鐘部程區內編線,到可連項輸出使能要單元,來自下一個宏單元 到下一個宏單元.

圖7.3.3 XC9500系列的乘積項分配和宏單元

來自可編程乘積項陣列的5個乘積項,通過數據分配器S1~S5送至宏單元的主或門G4構成與一或式。與此同時,或門G4最上端的輸人,可以通過數據分配器S6、S7和或門G3,取自上一個相鄰宏單元的乘積項或下一個相鄰宏單元的乘積項,從而擴展了乘積項的個數。

宏單元中任何沒有用到的乘積項,都可以經過或門Gl與經S6和S7來自相鄰宏單元的乘積項由或門G2組合在一起,再經過數據分配器S:送到上一個存儲器、復雜可編程器件和現場可編程門陣列.

選擇其來源其中,全局輸出使能控制信號有多個,不同型號的器件,其數量也不同(XC9500系列中r=4,MAX7000系列中r=6。當oE為低電平時,I/0引腳可用作輸入,引腳上的輸入信號經過輸入緩沖器送至內部可編程連線區。到其他I/o單元

輸入緩沖單元,圖7.3.5 I/o單元的簡化結構圖

圖7.3.5中D1和D2是鉗位二極管,用于I/0引腳的保護。另外,通過編程可以使I/o引腳接上拉電阻或接地,也可以控制輸出擺率(轉換速率SR),選擇快速方式可適應頻率較高的信號輸出,選擇慢速方式則可減小功耗和降低噪聲。ycclNT是器件內部邏輯電路的工作電壓(也稱為核心工作電壓①),而ycc的引入,可以使I/0引腳兼容多種電源系統。

CPLD編程簡介,通過上一節的介紹可以看出,CPLD的各種邏輯功能的實現,都是由其內部的可編程單元控制的。這些單元大多采用E2PROM或閃爍存儲器編程技術。

編程過程就是將編程數據寫入這些單元的過程。這一過程也稱為下載(Down~load)或酉己置(Configure)。

寫人CPLD中的編程數據都是由可編程器件的開發軟件自動生成的。用戶在開發軟仵中輸人設計及要求。利用開發軟件對設計進行檢查、分析和優化,系Core Vdtage的譯稱。到內部可編程連線區,來自宏單元全局輸出使能到其他I/o,存儲器、復雜可編程器件和現場可編程陣列.

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

公網安備44030402000607

公網安備44030402000607