CMOS數字輸出驅動器低壓差分信號LVDS

發布時間:2020/11/14 12:07:55 訪問次數:1018

模數轉換器(ADC)可以選擇,數字數據輸出類型是選擇過程中需要考慮的一項重要參數。目前,高速轉換器三種最常用的數字輸出是互補金屬氧化物半導體(CMOS)、低壓差分信號(LVDS)和電流模式邏輯(CML)。ADC中每種數字輸出類型都各有優劣,設計人員應根據特定應用仔細考慮。

這些因素取決于ADC的采樣速率和分辨率、輸出數據速率、系統設計的電源要求,以及其他因素。每種輸出類型的電氣規格,及其適合特定應用的具體特點。我們將從物理實現、效率以及最適合每種類型的應用這些方面來對比這些不同類型的輸出。

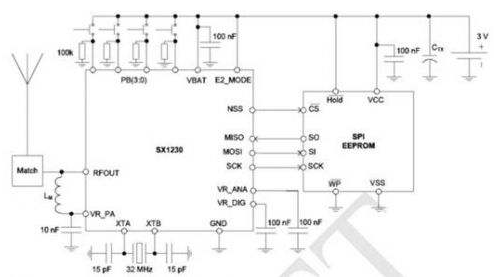

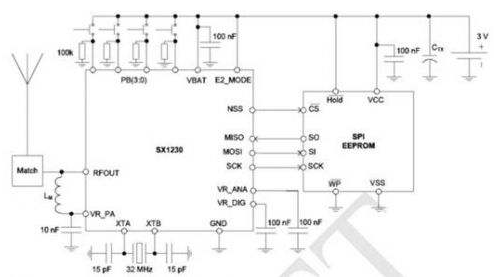

CMOS數字輸出驅動器,在采樣速率低于200 MSPS的ADC中,CMOS是很常見的數字輸出。典型的CMOS驅動器由兩個晶體管(一個NMOS和一個PMOS)組成,連接在電源(VDD)和地之間。這種結構會導致輸出反轉,背對背結構作為替代方法,避免輸出反轉。

ADC可以實現更高的動態范圍。過采樣的工作原理是假設噪聲源不相關且均值為零,這是因為樣本將白噪聲視為頻譜中均勻分布的噪聲,或者將以相鄰代碼為中心的高斯噪聲分布視為可通過平均來降低的信號。

使用AD7380所生成的快速傅立葉變換(FFT)曲線示例,分兩種情況:無過采樣和應用滾動平均過采樣,OSR = 8。

利用AD7380改善噪聲,本底噪聲有顯著改善,這與SNR的增加是一致的。在使能正常平均過采樣和滾動平均過采樣的情況下,SNR分別提高到96 dB和95 dB。

AD7380 SNR與過采樣率的關系,要評估應用過采樣技術所獲得的SNR改善情況,請使用以下公式:

其中:

N為ADC分辨率。

fs為采樣頻率。

BW為目標帶寬。

輸出為低阻抗時,CMOS輸出驅動器的輸入為高阻抗。在驅動器的輸入端,由于柵極與導電材料之間經柵極氧化層隔離,兩個CMOS晶體管的柵極阻抗極高。輸入端阻抗范圍可達kΩ至MΩ級。在驅動器輸出端,阻抗由漏電流ID控制,該電流通常較小。此時,阻抗通常小于幾百Ω。CMOS的電平擺幅大約在VDD和地之間,因此可能會很大,具體取決于VDD幅度。

典型CMOS數字輸出驅動器,由于輸入阻抗較高,輸出阻抗較低,CMOS的優勢之一在于通常可以用一個輸出驅動多個CMOS輸入。CMOS的另一個優勢是低靜態電流。唯一出現較大電流的情況是CMOS驅動器上發生切換時。

無論驅動器處于低電平(拉至地)還是高電平(拉至VDD),驅動器中的電流都極小。但是,當驅動器從低電平切換到高電平或從高電平切換到低電平時,VDD與地之間會暫時出現低阻抗路徑。

(素材來源:21ic.如涉版權請聯系刪除。特別感謝)

模數轉換器(ADC)可以選擇,數字數據輸出類型是選擇過程中需要考慮的一項重要參數。目前,高速轉換器三種最常用的數字輸出是互補金屬氧化物半導體(CMOS)、低壓差分信號(LVDS)和電流模式邏輯(CML)。ADC中每種數字輸出類型都各有優劣,設計人員應根據特定應用仔細考慮。

這些因素取決于ADC的采樣速率和分辨率、輸出數據速率、系統設計的電源要求,以及其他因素。每種輸出類型的電氣規格,及其適合特定應用的具體特點。我們將從物理實現、效率以及最適合每種類型的應用這些方面來對比這些不同類型的輸出。

CMOS數字輸出驅動器,在采樣速率低于200 MSPS的ADC中,CMOS是很常見的數字輸出。典型的CMOS驅動器由兩個晶體管(一個NMOS和一個PMOS)組成,連接在電源(VDD)和地之間。這種結構會導致輸出反轉,背對背結構作為替代方法,避免輸出反轉。

ADC可以實現更高的動態范圍。過采樣的工作原理是假設噪聲源不相關且均值為零,這是因為樣本將白噪聲視為頻譜中均勻分布的噪聲,或者將以相鄰代碼為中心的高斯噪聲分布視為可通過平均來降低的信號。

使用AD7380所生成的快速傅立葉變換(FFT)曲線示例,分兩種情況:無過采樣和應用滾動平均過采樣,OSR = 8。

利用AD7380改善噪聲,本底噪聲有顯著改善,這與SNR的增加是一致的。在使能正常平均過采樣和滾動平均過采樣的情況下,SNR分別提高到96 dB和95 dB。

AD7380 SNR與過采樣率的關系,要評估應用過采樣技術所獲得的SNR改善情況,請使用以下公式:

其中:

N為ADC分辨率。

fs為采樣頻率。

BW為目標帶寬。

輸出為低阻抗時,CMOS輸出驅動器的輸入為高阻抗。在驅動器的輸入端,由于柵極與導電材料之間經柵極氧化層隔離,兩個CMOS晶體管的柵極阻抗極高。輸入端阻抗范圍可達kΩ至MΩ級。在驅動器輸出端,阻抗由漏電流ID控制,該電流通常較小。此時,阻抗通常小于幾百Ω。CMOS的電平擺幅大約在VDD和地之間,因此可能會很大,具體取決于VDD幅度。

典型CMOS數字輸出驅動器,由于輸入阻抗較高,輸出阻抗較低,CMOS的優勢之一在于通常可以用一個輸出驅動多個CMOS輸入。CMOS的另一個優勢是低靜態電流。唯一出現較大電流的情況是CMOS驅動器上發生切換時。

無論驅動器處于低電平(拉至地)還是高電平(拉至VDD),驅動器中的電流都極小。但是,當驅動器從低電平切換到高電平或從高電平切換到低電平時,VDD與地之間會暫時出現低阻抗路徑。

(素材來源:21ic.如涉版權請聯系刪除。特別感謝)

上一篇:頻率的速率對輸入信號進行采樣

公網安備44030402000607

公網安備44030402000607