差分阻抗控制大切口靠近DC/DC塊電路板的內層布線

發布時間:2020/12/13 22:26:11 訪問次數:513

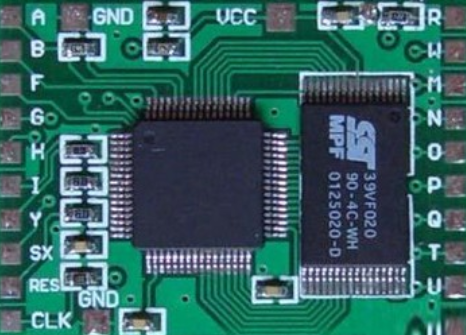

在電路板的內層布線,并在外層用銅屏蔽。當使用2層PCB時,通過在頂層和底層之間交替進行短長度布線。這種方法減少了每條記錄道的長度,使電路板對高頻干擾免疫。它還可以避免在兩層上對GND平面進行長距離切割。GND平面上的切割可以增加阻抗,并根據尺寸產生高頻噪聲。

在2層電路板中布線長跟蹤,在小型電路板中,元件靠近許多記錄道,通常使用通孔進行布線。確保有足夠的空間,使GND銅平面可以放置在通孔之間,同時避免大的切割。這是許多布局中常見的錯誤,當大切口靠近DC/DC塊時尤其危險。

制造商:Intel 產品種類:FPGA - 現場可編程門陣列 RoHS: 詳細信息 產品:Arria II GX 邏輯元件數量:60214 邏輯數組塊數量——LAB:2530 輸入/輸出端數量:364 I/O 工作電源電壓:1.5 V to 3.3 V 最小工作溫度:0 C 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-780 封裝:Tray 數據速率:600 Mb/s to 6.375 Gb/s 系列:Arria II GX 商標:Intel / Altera 自適應邏輯模塊 - ALM:25300 內嵌式塊RAM - EBR:791 kbit 嵌入式內存:5246 kbit 最大工作頻率:390 MHz 濕度敏感性:Yes 收發器數量:8 Transceiver 產品類型:FPGA - Field Programmable Gate Array 工廠包裝數量:36 子類別:Programmable Logic ICs 總內存:5246 kbit 商標名:Arria 零件號別名:971020 單位重量:3.300 g

差分走線一定要靠的很近。讓差分走線靠近無非是為了增強他們的耦合,既可以提高對噪聲的免疫力,還能充分利用磁場的相反極性來抵消對外界的電磁干擾。雖說這種做法在大多數情況下是非常有利的,但不是絕對的,如果能保證讓它們得到充分的屏蔽,不受外界干擾,那么我們也就不需要再讓通過彼此的強耦合達到抗干擾和抑制 EMI 的目的了。

如何才能保證差分走線具有良好的隔離和屏蔽,增大與其它信號走線的間距是最基本的途徑之一,電磁場能量是隨著距離呈平方關系遞減的,一般線間距超過4 倍線寬時,它們之間的干擾就極其微弱了,基本可以忽略。通過地平面的隔離也可以起到很好的屏蔽作用,這種結構在高頻的(10G 以上)IC封裝PCB 設計中經常會用采用,被稱為CPW結構,可以保證嚴格的差分阻抗控制(2Z0)。

(素材來源:ttic和21IC.如涉版權請聯系刪除。特別感謝)

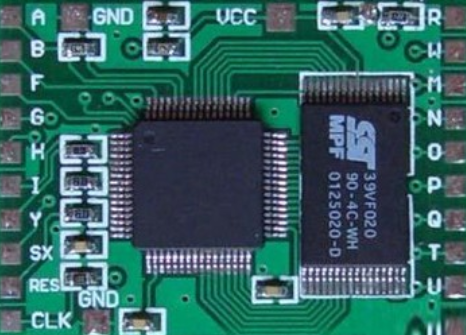

在電路板的內層布線,并在外層用銅屏蔽。當使用2層PCB時,通過在頂層和底層之間交替進行短長度布線。這種方法減少了每條記錄道的長度,使電路板對高頻干擾免疫。它還可以避免在兩層上對GND平面進行長距離切割。GND平面上的切割可以增加阻抗,并根據尺寸產生高頻噪聲。

在2層電路板中布線長跟蹤,在小型電路板中,元件靠近許多記錄道,通常使用通孔進行布線。確保有足夠的空間,使GND銅平面可以放置在通孔之間,同時避免大的切割。這是許多布局中常見的錯誤,當大切口靠近DC/DC塊時尤其危險。

制造商:Intel 產品種類:FPGA - 現場可編程門陣列 RoHS: 詳細信息 產品:Arria II GX 邏輯元件數量:60214 邏輯數組塊數量——LAB:2530 輸入/輸出端數量:364 I/O 工作電源電壓:1.5 V to 3.3 V 最小工作溫度:0 C 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-780 封裝:Tray 數據速率:600 Mb/s to 6.375 Gb/s 系列:Arria II GX 商標:Intel / Altera 自適應邏輯模塊 - ALM:25300 內嵌式塊RAM - EBR:791 kbit 嵌入式內存:5246 kbit 最大工作頻率:390 MHz 濕度敏感性:Yes 收發器數量:8 Transceiver 產品類型:FPGA - Field Programmable Gate Array 工廠包裝數量:36 子類別:Programmable Logic ICs 總內存:5246 kbit 商標名:Arria 零件號別名:971020 單位重量:3.300 g

差分走線一定要靠的很近。讓差分走線靠近無非是為了增強他們的耦合,既可以提高對噪聲的免疫力,還能充分利用磁場的相反極性來抵消對外界的電磁干擾。雖說這種做法在大多數情況下是非常有利的,但不是絕對的,如果能保證讓它們得到充分的屏蔽,不受外界干擾,那么我們也就不需要再讓通過彼此的強耦合達到抗干擾和抑制 EMI 的目的了。

如何才能保證差分走線具有良好的隔離和屏蔽,增大與其它信號走線的間距是最基本的途徑之一,電磁場能量是隨著距離呈平方關系遞減的,一般線間距超過4 倍線寬時,它們之間的干擾就極其微弱了,基本可以忽略。通過地平面的隔離也可以起到很好的屏蔽作用,這種結構在高頻的(10G 以上)IC封裝PCB 設計中經常會用采用,被稱為CPW結構,可以保證嚴格的差分阻抗控制(2Z0)。

(素材來源:ttic和21IC.如涉版權請聯系刪除。特別感謝)

公網安備44030402000607

公網安備44030402000607