»´◊g¥a∑®

∞l≤ºïrÈg:2014/6/3 20:46:07 ‘LÜñ¥Œîµ:7847

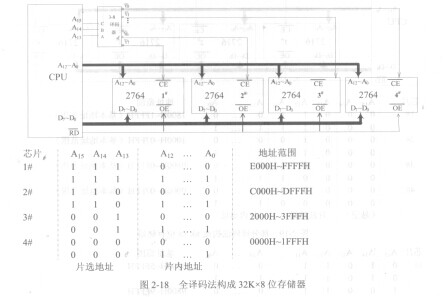

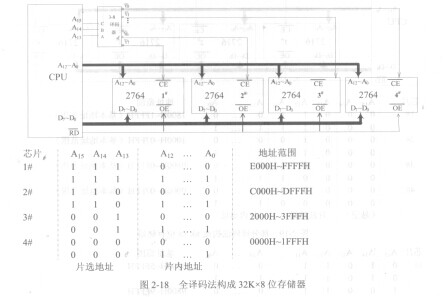

»´◊g¥a∑®µƒÃÿ¸c « π”√CPUµƒ»´≤ø∏þŒªµÿ÷∑æÄÖ¢≈c◊g¥a∆˜◊g¥a∫Û◊˜ûÈ¥Êɶ–æ∆¨µƒ∆¨þx–≈Ãñ°£SN74HC164DR¿˝»Á£¨”√4∆¨2764£®8Kx8Œª£©¥Êɶ–æ∆¨≤…”√»´◊g¥a∑®ΩM≥…32Kx8Œª¥Êɶ∆˜–æ∆¨ΩM£¨∆‰÷–∆¨É»µÿ÷∑æÄ13ól£¨ûÈAO°´A12£¨∆¨þxµÿ÷∑3ól»´≤øº”µΩ“ªÇÄ3-8◊g¥a∆˜…œ£¨»ÁàD2-18À˘ æ°£

àD2-18»´◊g¥a∑®òã≥…32Kx8Œª¥Êɶ∆˜

”…”⁄»´◊g¥a∑®÷–õ]”–µÿ÷∑æÄø’Èe£¨À˘“‘üo÷ÿØBµÿ÷∑∑∂á˙£¨√øÇÄ–æ∆¨µƒµÿ÷∑ «Œ®“ªµƒ°£∂¯«““≤õ]”–≤ªø… π”√µƒµÿ÷∑£¨å§÷∑∑∂á˙µ√µΩ≥‰∑÷¿˚”√°£»Á‘⁄…œ¿˝÷–îU’πµΩ32Kx8Œª∫Û£¨»‘”–56Kµÿ÷∑ø…π©þM“ª≤ΩîU’π°£µ´»´◊g¥a∑®À˘–˵ƒ◊g¥aÎä¬∑±»ð^èÕÎs£¨‘⁄“ª–©–æ∆¨»ð¡ø∫Ж°£¨∆¨þxµÿ÷∑æÄ∫Ð∂ýµƒàˆ∫œø…“‘≤…”√÷ª”–≤ø∑÷∆¨þxæÄÖ¢≈c◊g¥aµƒ∑Ω∑®£¨º¥ûÈ≤ø∑÷◊g¥a∑®°£

»´◊g¥a∑®µƒÃÿ¸c « π”√CPUµƒ»´≤ø∏þŒªµÿ÷∑æÄÖ¢≈c◊g¥a∆˜◊g¥a∫Û◊˜ûÈ¥Êɶ–æ∆¨µƒ∆¨þx–≈Ãñ°£SN74HC164DR¿˝»Á£¨”√4∆¨2764£®8Kx8Œª£©¥Êɶ–æ∆¨≤…”√»´◊g¥a∑®ΩM≥…32Kx8Œª¥Êɶ∆˜–æ∆¨ΩM£¨∆‰÷–∆¨É»µÿ÷∑æÄ13ól£¨ûÈAO°´A12£¨∆¨þxµÿ÷∑3ól»´≤øº”µΩ“ªÇÄ3-8◊g¥a∆˜…œ£¨»ÁàD2-18À˘ æ°£

àD2-18»´◊g¥a∑®òã≥…32Kx8Œª¥Êɶ∆˜

”…”⁄»´◊g¥a∑®÷–õ]”–µÿ÷∑æÄø’Èe£¨À˘“‘üo÷ÿØBµÿ÷∑∑∂á˙£¨√øÇÄ–æ∆¨µƒµÿ÷∑ «Œ®“ªµƒ°£∂¯«““≤õ]”–≤ªø… π”√µƒµÿ÷∑£¨å§÷∑∑∂á˙µ√µΩ≥‰∑÷¿˚”√°£»Á‘⁄…œ¿˝÷–îU’πµΩ32Kx8Œª∫Û£¨»‘”–56Kµÿ÷∑ø…π©þM“ª≤ΩîU’π°£µ´»´◊g¥a∑®À˘–˵ƒ◊g¥aÎä¬∑±»ð^èÕÎs£¨‘⁄“ª–©–æ∆¨»ð¡ø∫Ж°£¨∆¨þxµÿ÷∑æÄ∫Ð∂ýµƒàˆ∫œø…“‘≤…”√÷ª”–≤ø∑÷∆¨þxæÄÖ¢≈c◊g¥aµƒ∑Ω∑®£¨º¥ûÈ≤ø∑÷◊g¥a∑®°£

…œ“ª∆™£∫6264–æ∆¨µƒµÿ÷∑∑∂á˙

…œ“ª∆™£∫≤ø∑÷◊g¥a∑®

ü·ÈT¸cìÙ

ü·ÈT¸cìÙ

- »´◊g¥a∑®

- ±£◊CŸN—bŸ|¡øµƒ»˝“™Àÿ

- ”|◊É÷∏îµ∫ÕÀ˙¬‰∂»

- þ\”√∫∏Ω”¿Ì’ì’˝¥_‘O÷√üo„U‘Ÿ¡˜∫∏úÿ∂»«˙æÄ

- ±Ì√ÊŸN—b‘™∆˜º˛–Þ∞Â≈c∑µ–Þπ§Àá

- Õ¨ðSÎä¿|∫ÕÎpΩgæÄ

- Îä¥≈ºÊ»ð–‘‘O”ã

Õ∆À]ºº–gŸY¡œ

Õ∆À]ºº–gŸY¡œ

- ÷–á¯Ç˜√Ω¥ÛåWǘ√Ω≤©ŒÔ^È_

- ǘ√Ω≤©ŒÔ^È_^Éx Ω¬°ÕØ≈e––°£ΩÔ˝∂ºi᯺“èVÎäøÇæ÷µ»≤øÈT... [‘îºö]

- ƒ£îM∫ÕªÏ∫œ–≈Ãñ∆Ω≈_Treo‘î«È

- PXI∫ÕLXIƒ£âKªØΩ‚õQ∑Ω∞∏Ω‚◊x

- AN-13-0004_CAN ’∞l∆˜ΩYòãÖ¢îµÃÿ

- ∆¡±Œñ≈≤€úœºº–g (SGT)&#

- µ⁄“ª¥˙SGT MOSFETœµ¡–ºº–gΩYòãÖ¢îµ∑‚

- »´«Ú ◊ÓwGSE DPU–æ∆¨∞l≤º

- ∂ý√ΩÛwÖfÃé¿Ì∆˜SM501‘⁄«∂»Î ΩœµΩy÷–µƒë™”√

- ª˘”⁄IEEE802.11bµƒEPAúÿ∂»◊ÉÀÕ∆˜

- QUICCEngine–¬“˝«ÊÕ∆Ñ”IPæWΩj∏Ô–¬

- SoC√Ê ¿∞ÀƒÍ∫ÛµƒÆaòIôC”ˆ

- MPC8xxœµ¡–Ãé¿Ì∆˜µƒ«∂»Î ΩœµΩyÎä‘¥‘O”ã

- dsPICº∞∆‰‘⁄Ωª¡˜◊ÉÓl’{ÀŸ÷–µƒë™”√—–æø

π´æW∞≤lj44030402000607

π´æW∞≤lj44030402000607