CⅤD工藝方法的進展

發布時間:2017/5/19 21:25:35 訪問次數:1041

集成電路工藝中除了采用上述3種CVD方法制備薄膜之外,還有熱絲化學氣相淀積(HWCⅥ⑵、MOCVD、等。CXJD薄膜制各工藝方法的進展,一方面是常規LPCVD和PECVD技術的進步,這主要表現在工藝設備的發展完善,如HDRCVD等;另-方面是新工藝方法在集成電路工藝中的應用,如HWCVD等。 K4B1G0846G-BCH9

高密度等離子體化學氣相淀積

高密度等離子體化學氣相淀積(I】DP60)是在PEC、0基礎上發展起來的新技術,在⒛世紀∞年代中期才得到了廣泛應用。它的主要特點是淀積薄膜的臺階覆蓋特性好,即使淀積溫度只有3O0~⑽0℃,也能磁場線圈 在有高深寬比微結構的襯底上制備出有較好臺階覆

蓋效果的薄膜。因此,它常用于集成電路淺槽隔離工藝的介質薄膜淀積,以及多層金屬化系統中的層間介質薄膜和低乃介質薄膜的淀積。

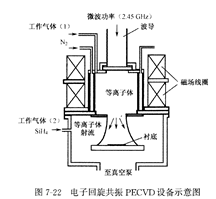

圖⒎22所示是電子回旋共振PECˇD設備示意圖。微波功率(2,45GHz)導人等離子體室,工作氣體(1)為氮氣(N2)。由于特定磁場的存在,自由電子在等離子室中回旋共振,因此,在等離子室中形成含 高密度N+的等離子體。而I作氣體(2)為硅烷,直接進人襯底淀積室,激發形成等離子體。襯底硅片放在淀積室電極上,由于等離子鞘現象,相對于等離子體而言電為低電位,含高密度Ni的等離子體從窗口射人直達襯底,氮氣和硅烷兩等離子體混合,在襯底淀積出氮化硅薄膜,同時由于N+的轟擊、濺射,使得淀積的氮化硅薄膜可以填充深寬比為3:1到4:1,甚至更大的孔洞和溝槽。應用HDP CVD淀積薄膜的質量與速率不僅與等離子源的性質相關,還與反應腔室的結構及細節設計有很大關系。

集成電路工藝中除了采用上述3種CVD方法制備薄膜之外,還有熱絲化學氣相淀積(HWCⅥ⑵、MOCVD、等。CXJD薄膜制各工藝方法的進展,一方面是常規LPCVD和PECVD技術的進步,這主要表現在工藝設備的發展完善,如HDRCVD等;另-方面是新工藝方法在集成電路工藝中的應用,如HWCVD等。 K4B1G0846G-BCH9

高密度等離子體化學氣相淀積

高密度等離子體化學氣相淀積(I】DP60)是在PEC、0基礎上發展起來的新技術,在⒛世紀∞年代中期才得到了廣泛應用。它的主要特點是淀積薄膜的臺階覆蓋特性好,即使淀積溫度只有3O0~⑽0℃,也能磁場線圈 在有高深寬比微結構的襯底上制備出有較好臺階覆

蓋效果的薄膜。因此,它常用于集成電路淺槽隔離工藝的介質薄膜淀積,以及多層金屬化系統中的層間介質薄膜和低乃介質薄膜的淀積。

圖⒎22所示是電子回旋共振PECˇD設備示意圖。微波功率(2,45GHz)導人等離子體室,工作氣體(1)為氮氣(N2)。由于特定磁場的存在,自由電子在等離子室中回旋共振,因此,在等離子室中形成含 高密度N+的等離子體。而I作氣體(2)為硅烷,直接進人襯底淀積室,激發形成等離子體。襯底硅片放在淀積室電極上,由于等離子鞘現象,相對于等離子體而言電為低電位,含高密度Ni的等離子體從窗口射人直達襯底,氮氣和硅烷兩等離子體混合,在襯底淀積出氮化硅薄膜,同時由于N+的轟擊、濺射,使得淀積的氮化硅薄膜可以填充深寬比為3:1到4:1,甚至更大的孔洞和溝槽。應用HDP CVD淀積薄膜的質量與速率不僅與等離子源的性質相關,還與反應腔室的結構及細節設計有很大關系。

上一篇:原子基團是非常活潑的激活態物質

上一篇:熱絲化學氣相淀積

熱門點擊

熱門點擊

公網安備44030402000607

公網安備44030402000607