OR2T06A4T100-DB 時序邏輯電路的模型與分類

發布時間:2020/1/17 13:12:13 訪問次數:2057

OR2T06A4T100-DB用Verilog HDL描述鎖存器和觸發器,試說明下列程序所完成的邏輯功能,并畫出它的邏輯圖。

試用Vehlog HDL行為級建模方式描述一個下降沿觸發的D觸發器,要求具有日常生活中,時序邏輯的實例并不鮮見,例如樓房電梯的控制便是一個典型的時序邏輯問題。電梯的控制電路需要根據電梯內和各樓層入口處的按鍵信號,以及電梯當前的狀態來決定電梯的升降,同時將電梯當前所處樓層信號輸出到電梯內外。這里,按鍵信號和所到達的樓層信號是時序邏輯的“輸入信號”,升降信號和到達樓層的顯示則是其“輸出信號”。顯然,控制電路中必須具有存儲單元,以記憶當前電梯所在的樓層。可以定義電梯目前所處樓層為現在的狀態,簡稱“現態”,將要到達的樓層為下一個狀態,簡稱“次態”,樓層的變換即為“狀態轉換”。由于電梯的升降不僅取決于當前各按鍵的輸人信號,而且取決于電梯運轉的歷史狀態,例如電梯是從更低的樓層升上來的,若這時電梯內已有人按下更高樓層的按鍵,或更高的樓層有人召喚,電梯則應向高一層轉換其狀態而暫時忽略電梯內要求下樓的按鍵輸入或低樓層的召喚信號。這種確定電梯狀態如何轉換的信號稱為“激勵信號”。

諸如上例中的輸人信號、輸出信號、激勵信號以及現態、次態及其狀態轉換的關系是時序邏輯電路研究的主要內容。

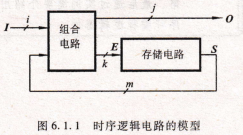

時序邏輯電路的模型與分類,時序電路的模型,上述電梯控制的實例可以用如圖6.1.1所示時序電路的一般化模型來表示。從總體上看,整個時序電路由進行邏輯運算的組合電路和起記憶r作用的存儲電路兩部分構成,存儲電路可用觸發器或鎖存器組成。為了方便,圖中各組變量均以向量表示,其中,r=(r,f,…,fi)為時序電路的輸人信號,0=(01,02,…, 圖6.1.1 時序邏輯電路的模型a)為時序電路的輸出信號,E=(E”E2,…,E滋)為驅動存儲電路轉換為下一狀態的激勵信號,而s=(s1,S2,…,sm)為存儲電路的狀態信號,亦稱為狀態變量,它表示時序電路當前的狀態,簡稱現態。狀態變量s被反饋到組合電路.

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

OR2T06A4T100-DB用Verilog HDL描述鎖存器和觸發器,試說明下列程序所完成的邏輯功能,并畫出它的邏輯圖。

試用Vehlog HDL行為級建模方式描述一個下降沿觸發的D觸發器,要求具有日常生活中,時序邏輯的實例并不鮮見,例如樓房電梯的控制便是一個典型的時序邏輯問題。電梯的控制電路需要根據電梯內和各樓層入口處的按鍵信號,以及電梯當前的狀態來決定電梯的升降,同時將電梯當前所處樓層信號輸出到電梯內外。這里,按鍵信號和所到達的樓層信號是時序邏輯的“輸入信號”,升降信號和到達樓層的顯示則是其“輸出信號”。顯然,控制電路中必須具有存儲單元,以記憶當前電梯所在的樓層。可以定義電梯目前所處樓層為現在的狀態,簡稱“現態”,將要到達的樓層為下一個狀態,簡稱“次態”,樓層的變換即為“狀態轉換”。由于電梯的升降不僅取決于當前各按鍵的輸人信號,而且取決于電梯運轉的歷史狀態,例如電梯是從更低的樓層升上來的,若這時電梯內已有人按下更高樓層的按鍵,或更高的樓層有人召喚,電梯則應向高一層轉換其狀態而暫時忽略電梯內要求下樓的按鍵輸入或低樓層的召喚信號。這種確定電梯狀態如何轉換的信號稱為“激勵信號”。

諸如上例中的輸人信號、輸出信號、激勵信號以及現態、次態及其狀態轉換的關系是時序邏輯電路研究的主要內容。

時序邏輯電路的模型與分類,時序電路的模型,上述電梯控制的實例可以用如圖6.1.1所示時序電路的一般化模型來表示。從總體上看,整個時序電路由進行邏輯運算的組合電路和起記憶r作用的存儲電路兩部分構成,存儲電路可用觸發器或鎖存器組成。為了方便,圖中各組變量均以向量表示,其中,r=(r,f,…,fi)為時序電路的輸人信號,0=(01,02,…, 圖6.1.1 時序邏輯電路的模型a)為時序電路的輸出信號,E=(E”E2,…,E滋)為驅動存儲電路轉換為下一狀態的激勵信號,而s=(s1,S2,…,sm)為存儲電路的狀態信號,亦稱為狀態變量,它表示時序電路當前的狀態,簡稱現態。狀態變量s被反饋到組合電路.

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

公網安備44030402000607

公網安備44030402000607