浪涌電壓全環路DRAM結構的單個器件進行了電氣分析

發布時間:2021/8/31 0:44:29 訪問次數:219

埋入式字線的DRAM單元中,晶體管通道位于鰭片中部附近,這里的形狀扭曲要比鰭片頂部嚴重。在這種情況下,受側壁鈍化的影響,該通道下方的鰭片CD也要大很多。

為評估AA形狀扭曲對器件性能的影響,我們用SEMulator3D建模了0.1、2.5和5度的側壁裂角以模擬不同程度的AA扭曲,并使用來自全環路DRAM結構的單個器件進行了電氣分析。

通過SEMulator3D分配電端口(源極、漏極、柵極和襯底)即可獲得電氣測量值,之后使用SEMulator3D內置漂移/擴散求解器即可計算不同程度AA扭曲可能導致的電氣性能變化。

制造商:Xilinx產品種類:FPGA - 現場可編程門陣列RoHS:產品:Virtex-5系列:XC5VFX130T邏輯元件數量:131072 LE自適應邏輯模塊 - ALM:20480 ALM嵌入式內存:10.48 Mbit輸入/輸出端數量:840 I/O工作電源電壓:1 V最小工作溫度:- 40 C最大工作溫度:+ 100 C安裝風格:SMD/SMT封裝 / 箱體:FCBGA-1738數據速率:6.5 Gb/s商標:Xilinx分布式RAM:1580 kbit內嵌式塊RAM - EBR:10728 kbit最大工作頻率:550 MHz濕度敏感性:Yes邏輯數組塊數量——LAB:10240 LAB收發器數量:20 Transceiver產品類型:FPGA - Field Programmable Gate Array工廠包裝數量:1子類別:Programmable Logic ICs商標名:Virtex

通過這種建模技術,我們可以創建DRAM器件的3D模型并模擬出AA形狀扭曲現象。通過SEMulator3D模擬的DRAM 3D結構和平面圖、布局設計和圖形相關掩膜。

通過對比可以看出,AA扭曲形態是類似的,這證明模型能正確反映實際制造結果。不同鰭片高度的AA剖面圖,從中可以看出結構底部的扭曲幅度要遠高于器件頂部的扭曲。

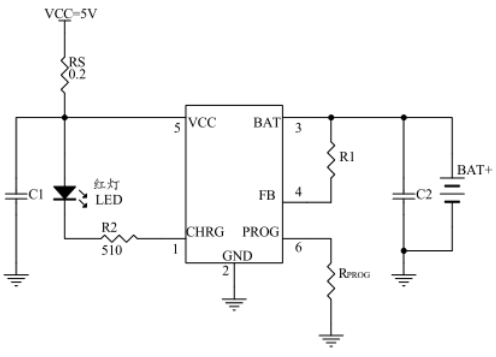

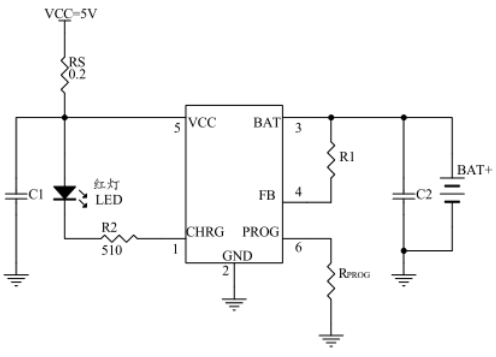

當線路上出現浪涌電壓時,浪涌抑制器就會起作用,把浪涌能量旁路到大地,浪涌電流(可達幾千安培)就會在地線上產生電壓,這種電壓可以很高,甚至會達到干擾數字電路的程度。

(素材來源:eccn和ttic.如涉版權請聯系刪除。特別感謝)

埋入式字線的DRAM單元中,晶體管通道位于鰭片中部附近,這里的形狀扭曲要比鰭片頂部嚴重。在這種情況下,受側壁鈍化的影響,該通道下方的鰭片CD也要大很多。

為評估AA形狀扭曲對器件性能的影響,我們用SEMulator3D建模了0.1、2.5和5度的側壁裂角以模擬不同程度的AA扭曲,并使用來自全環路DRAM結構的單個器件進行了電氣分析。

通過SEMulator3D分配電端口(源極、漏極、柵極和襯底)即可獲得電氣測量值,之后使用SEMulator3D內置漂移/擴散求解器即可計算不同程度AA扭曲可能導致的電氣性能變化。

制造商:Xilinx產品種類:FPGA - 現場可編程門陣列RoHS:產品:Virtex-5系列:XC5VFX130T邏輯元件數量:131072 LE自適應邏輯模塊 - ALM:20480 ALM嵌入式內存:10.48 Mbit輸入/輸出端數量:840 I/O工作電源電壓:1 V最小工作溫度:- 40 C最大工作溫度:+ 100 C安裝風格:SMD/SMT封裝 / 箱體:FCBGA-1738數據速率:6.5 Gb/s商標:Xilinx分布式RAM:1580 kbit內嵌式塊RAM - EBR:10728 kbit最大工作頻率:550 MHz濕度敏感性:Yes邏輯數組塊數量——LAB:10240 LAB收發器數量:20 Transceiver產品類型:FPGA - Field Programmable Gate Array工廠包裝數量:1子類別:Programmable Logic ICs商標名:Virtex

通過這種建模技術,我們可以創建DRAM器件的3D模型并模擬出AA形狀扭曲現象。通過SEMulator3D模擬的DRAM 3D結構和平面圖、布局設計和圖形相關掩膜。

通過對比可以看出,AA扭曲形態是類似的,這證明模型能正確反映實際制造結果。不同鰭片高度的AA剖面圖,從中可以看出結構底部的扭曲幅度要遠高于器件頂部的扭曲。

當線路上出現浪涌電壓時,浪涌抑制器就會起作用,把浪涌能量旁路到大地,浪涌電流(可達幾千安培)就會在地線上產生電壓,這種電壓可以很高,甚至會達到干擾數字電路的程度。

(素材來源:eccn和ttic.如涉版權請聯系刪除。特別感謝)

公網安備44030402000607

公網安備44030402000607