門電路的模擬利測試

發布時間:2016/7/2 18:32:02 訪問次數:391

cMOs電路有P管網絡和N管網絡,化。由于空穴的碰撞離化率比電子小得多,AD8042AR兩者都存在熱載流子注入效應引起的退所以相同應力條件下P管比N管的熱載流子退化也要小很多。電路設計上可以忽略PMOS管的熱載流子注入效應引起的退化,僅考慮NMOS管的熱載流子注入效應引起的退化。

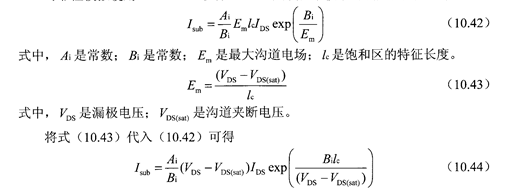

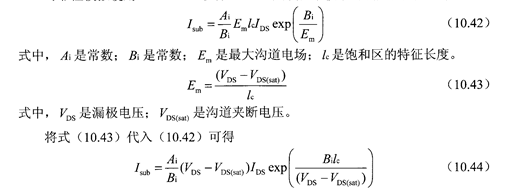

在或非門電路中,多個NMOs管的并聯使每個NMOS管上的漏源電壓都一樣大;而CMOs與非門中,所有NMOS管串聯接在輸出節點與地之間,當輸出負載電容放電時,最靠近輸出節點的NMOS晶體管,即頂端NMOS管承受高漏源電壓的時間最長,承受的應力最大,因而最易發生退化。可靠性模擬使用BTABERT軟件,MOS熱載流子模擬時調用襯底電流模型:

cMOs電路有P管網絡和N管網絡,化。由于空穴的碰撞離化率比電子小得多,AD8042AR兩者都存在熱載流子注入效應引起的退所以相同應力條件下P管比N管的熱載流子退化也要小很多。電路設計上可以忽略PMOS管的熱載流子注入效應引起的退化,僅考慮NMOS管的熱載流子注入效應引起的退化。

在或非門電路中,多個NMOs管的并聯使每個NMOS管上的漏源電壓都一樣大;而CMOs與非門中,所有NMOS管串聯接在輸出節點與地之間,當輸出負載電容放電時,最靠近輸出節點的NMOS晶體管,即頂端NMOS管承受高漏源電壓的時間最長,承受的應力最大,因而最易發生退化。可靠性模擬使用BTABERT軟件,MOS熱載流子模擬時調用襯底電流模型:

上一篇:可靠性模擬時調用襯底電流模型

公網安備44030402000607

公網安備44030402000607