ІўВ“лҠИЭ

°lІј•rйg:2017/6/22 19:52:19 ФLҶ–ҙО”ө:1126

УРР§өДИЭРФИҘсоКЗНЁЯ^ФЪPCBЙПЯm®”·ЕЦГлҠИЭҒнҢҚ¬FөДЎЈлSТв·ЕЦГ»тЯ^¶ИК№УГлҠИЭКЗҢҰІДБПөДАЛЩMЎЈУР•r‘рВФРФөШ·ЕҺЧӮҖлҠИЭҢўЖрөҪәЬәГөДИҘсоР§№ыЎЈM25P20-VMN6TPBФЪҢҚлHөД‘ӘУГЦР,ғЙӮҖлҠИЭІўВ“К№УГДЬМṩёьҢ’өДТЦЦЖҺ§Ң’ЎЈЯ@ғЙӮҖІўВ“лҠИЭұШнҡУРІ»Н¬өД”өБҝјү(Из0.1uFәН0.001uF)»тИЭЦөПаІо100ұ¶өДкPПө,ТФЯ_өҪЧојСөДР§№ыЎЈ

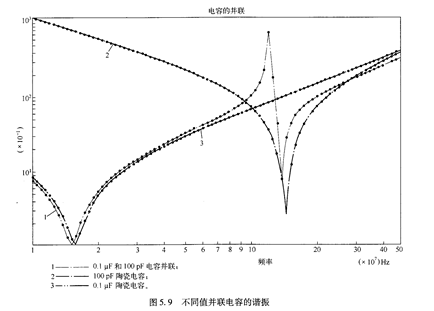

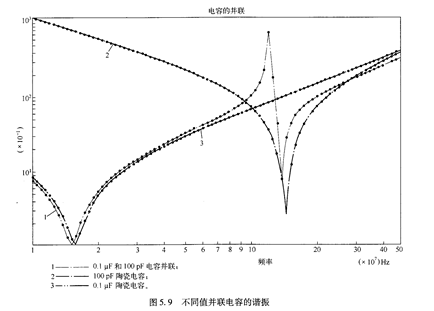

ҲD5.9п@КҫБЛ0.1uFәН100pFғЙӮҖИҘсолҠИЭҶОӘҡК№УГәНІўВ“К№УГөДЗъҫҖЎЈ0,1uFлҠИЭөДЧФЦCХсоlВКһй14.Ss MHz,100pFлҠИЭөДЧФЦCХсоlВККЗ148,5MHzЎЈФЪ110MHzЙП,ТтһйІўВ“лҠИЭөДҪYәПЧиҝ№УРТ»ӮҖәЬҙуөДЙПЙэ,0.1uFлҠИЭЧғіЙБЛёРРФөД,¶ш100pFөДлҠИЭИФһйИЭРФЎЈФЪЯ@ӮҖоlВК·¶ҮъғИҙжФЪТ»ӮҖІўВ“ЦCХсLCлҠВ·ЎЈФЪЦCХс•rјИУРлҠёРТІУРлҠИЭ,ТтҙЛ,•юУРТ»ӮҖ·ҙ№ІХсоlВКьc,ФЪЯ@Р©ЦCХсьcЦЬҮъ,ІўВ“лҠИЭұн¬FөДЧиҝ№ТӘҙуУЪЛь ӮғҶОӮҖК№УГ•rөДЧиҝ№,Из№ыФЪЯ@ӮҖьcёҪҪьТ»¶ЁТӘқMЧгEMIТӘЗу,Я@ҢўКЗӮҖпLлUЎЈ

ҝЙТҠ,һйБЛИҘіэҺ§Ң’Э^Ң’өДФлВ•,іЈУГөД·Ҫ·ЁКЗФЪҝҝҪьлҠФҙТэД_өДөШ·Ҫ·ЕЦГғЙӮҖІўВ“лҠИЭ(Из0.1uFәН0ЎЈЎЮ1uF)ЎЈИз№ыФЪPCBІјҫЦЦРК№УГІўВ“лҠИЭИҘсо,Т»¶ЁТӘұЈЧCлҠИЭЦөПаІоғЙӮҖ”өБҝјү»т1ЎЮұ¶ЎЈІўВ“лҠИЭөД`ҝӮИЭЦөІ»КЗЦчТӘөД,ЦШТӘөДТтЛШКЗУЙІўВ“лҠИЭ®aЙъөДІўВ“Чиҝ№ЎЈһйБЛғһ»ҜІўВ“ИҘсоөДР§№ыәНФКФSК№УГҶОӮҖлҠИЭ,РиТӘңpРЎлҠИЭғИөДТэҫҖлҠёРЎЈФЪлҠИЭСbөҪPCBЙП•r•юУРТ»¶ЁЦөөДІјҫҖлҠёРҙжФЪЎЈЯ@ӮҖҫҖйL°ьАЁЯBҪУлҠИЭөҪЖҪГжөДЯ^ҝЧөДйL¶ИЎЈҶОӮҖ»тІўВ“ИҘсолҠИЭөДТэҫҖФҪ¶М,ИҘсоР§№ыҫНФҪәГЎЈ

БнНв,ғЙӮҖН¬ЦөөДлҠИЭІўВ“,ТІҝЙТФМбёЯИҘсоөДР§№ыәНоlВК,Я@КЗТтһйлҠИЭІўВ“әујДЙълҠЧи(ESR)әНјДЙълҠёР(ESL)ТтІўВ“¶шңpРЎ,ҢҰУЪ¶аӮҖ(ЖЁ)Н¬ҳУЦөөДИЭҒнХf,ІўВ“К№УГЦ®әу,өИР§лҠИЭCЧғһйДбC,өИР§лҠёРLЧғһйЎЁө¶,өИР§EsRЧғһйR//L,ө«ЦCХсоlВКІ»ЧғЎЈН¬•rҸДДЬБҝөДҪЗ¶Иҝҙ,¶аӮҖлҠИЭІўВ“ҢўДЬПтұ»ИҘсоөДЖчШхМṩёь¶аөДДЬБҝ(ИзҲD5.10ЛщКҫ)ЎЈ

УРР§өДИЭРФИҘсоКЗНЁЯ^ФЪPCBЙПЯm®”·ЕЦГлҠИЭҒнҢҚ¬FөДЎЈлSТв·ЕЦГ»тЯ^¶ИК№УГлҠИЭКЗҢҰІДБПөДАЛЩMЎЈУР•r‘рВФРФөШ·ЕҺЧӮҖлҠИЭҢўЖрөҪәЬәГөДИҘсоР§№ыЎЈM25P20-VMN6TPBФЪҢҚлHөД‘ӘУГЦР,ғЙӮҖлҠИЭІўВ“К№УГДЬМṩёьҢ’өДТЦЦЖҺ§Ң’ЎЈЯ@ғЙӮҖІўВ“лҠИЭұШнҡУРІ»Н¬өД”өБҝјү(Из0.1uFәН0.001uF)»тИЭЦөПаІо100ұ¶өДкPПө,ТФЯ_өҪЧојСөДР§№ыЎЈ

ҲD5.9п@КҫБЛ0.1uFәН100pFғЙӮҖИҘсолҠИЭҶОӘҡК№УГәНІўВ“К№УГөДЗъҫҖЎЈ0,1uFлҠИЭөДЧФЦCХсоlВКһй14.Ss MHz,100pFлҠИЭөДЧФЦCХсоlВККЗ148,5MHzЎЈФЪ110MHzЙП,ТтһйІўВ“лҠИЭөДҪYәПЧиҝ№УРТ»ӮҖәЬҙуөДЙПЙэ,0.1uFлҠИЭЧғіЙБЛёРРФөД,¶ш100pFөДлҠИЭИФһйИЭРФЎЈФЪЯ@ӮҖоlВК·¶ҮъғИҙжФЪТ»ӮҖІўВ“ЦCХсLCлҠВ·ЎЈФЪЦCХс•rјИУРлҠёРТІУРлҠИЭ,ТтҙЛ,•юУРТ»ӮҖ·ҙ№ІХсоlВКьc,ФЪЯ@Р©ЦCХсьcЦЬҮъ,ІўВ“лҠИЭұн¬FөДЧиҝ№ТӘҙуУЪЛь ӮғҶОӮҖК№УГ•rөДЧиҝ№,Из№ыФЪЯ@ӮҖьcёҪҪьТ»¶ЁТӘқMЧгEMIТӘЗу,Я@ҢўКЗӮҖпLлUЎЈ

ҝЙТҠ,һйБЛИҘіэҺ§Ң’Э^Ң’өДФлВ•,іЈУГөД·Ҫ·ЁКЗФЪҝҝҪьлҠФҙТэД_өДөШ·Ҫ·ЕЦГғЙӮҖІўВ“лҠИЭ(Из0.1uFәН0ЎЈЎЮ1uF)ЎЈИз№ыФЪPCBІјҫЦЦРК№УГІўВ“лҠИЭИҘсо,Т»¶ЁТӘұЈЧCлҠИЭЦөПаІоғЙӮҖ”өБҝјү»т1ЎЮұ¶ЎЈІўВ“лҠИЭөД`ҝӮИЭЦөІ»КЗЦчТӘөД,ЦШТӘөДТтЛШКЗУЙІўВ“лҠИЭ®aЙъөДІўВ“Чиҝ№ЎЈһйБЛғһ»ҜІўВ“ИҘсоөДР§№ыәНФКФSК№УГҶОӮҖлҠИЭ,РиТӘңpРЎлҠИЭғИөДТэҫҖлҠёРЎЈФЪлҠИЭСbөҪPCBЙП•r•юУРТ»¶ЁЦөөДІјҫҖлҠёРҙжФЪЎЈЯ@ӮҖҫҖйL°ьАЁЯBҪУлҠИЭөҪЖҪГжөДЯ^ҝЧөДйL¶ИЎЈҶОӮҖ»тІўВ“ИҘсолҠИЭөДТэҫҖФҪ¶М,ИҘсоР§№ыҫНФҪәГЎЈ

БнНв,ғЙӮҖН¬ЦөөДлҠИЭІўВ“,ТІҝЙТФМбёЯИҘсоөДР§№ыәНоlВК,Я@КЗТтһйлҠИЭІўВ“әујДЙълҠЧи(ESR)әНјДЙълҠёР(ESL)ТтІўВ“¶шңpРЎ,ҢҰУЪ¶аӮҖ(ЖЁ)Н¬ҳУЦөөДИЭҒнХf,ІўВ“К№УГЦ®әу,өИР§лҠИЭCЧғһйДбC,өИР§лҠёРLЧғһйЎЁө¶,өИР§EsRЧғһйR//L,ө«ЦCХсоlВКІ»ЧғЎЈН¬•rҸДДЬБҝөДҪЗ¶Иҝҙ,¶аӮҖлҠИЭІўВ“ҢўДЬПтұ»ИҘсоөДЖчШхМṩёь¶аөДДЬБҝ(ИзҲD5.10ЛщКҫ)ЎЈ

ЙПТ»ЖӘЈәИҘсоәНЕФВ·лҠИЭөДЯx“с

ЙПТ»ЖӘЈәлҠИЭЦөҙуРЎҢҰлҠФҙИҘсоР§№ыөДУ°н‘

ҹбйTьc“ф

ҹбйTьc“ф

- өӘ»Ҝ№иұЎДӨРФЩ|ЕcУГНҫ

- Я…ҪзҢУәс¶ИЦчТӘКЬҡвуwүәБҰәНҡвБч о‘B(»тБчЛЩ)

- ¶юСх»Ҝ№иөДёЙ·ЁҝМОg

- үәәё

- PўхDёЕКц

- ¶аҫ§№иөДёЙ·ЁҝМОg

- ІўВ“лҠИЭ

- ЖБұОлҠА|өДЖБұОҢУТ»¶ЁТӘ360ЎгҙоҪУМҺАн

- һVІЁлҠВ·ёьёДәуөДлҠФҙ¶ЛҝЪӮчҢ§т}”_ңyФҮоlЧV

- EMCңyФҮөДҢҚЩ|

НЖЛ]јјРgЩYБП

НЖЛ]јјРgЩYБП

- ЧФЦЖҪӣөдөД1875№Ұ·Е

- ЖҪ•rОТТІҪӣіЈ№дТ»Р©Тфн‘DIYХ“үҜЈ¬°l¬FУРәЬ¶аИЛПІҡgLM... [Ф”јҡ]

- ДЈ”MәН»мәПРЕМ–ЖҪЕ_TreoФ”Зй

- PXIәНLXIДЈүK»ҜҪвӣQ·Ҫ°ёҪвЧx

- AN-13-0004_CANКХ°lЖчҪYҳӢ…ў”өМШ

- ЖБұО–ЕІЫңПјјРg (SGT)&#

- өЪТ»ҙъSGT MOSFETПөБРјјРgҪYҳӢ…ў”ө·в

- И«ЗтКЧоwGSE DPUРҫЖ¬°lІј

- ¶аГҪуw…fМҺАнЖчSM501ФЪЗ¶ИлКҪПөҪyЦРөД‘ӘУГ

- »щУЪIEEE802.11bөДEPAңШ¶ИЧғЛНЖч

- QUICCEngineРВТэЗжНЖ„УIPҫWҪjёпРВ

- SoCГжКА°ЛДкәуөД®aҳIҷCУц

- MPC8xxПөБРМҺАнЖчөДЗ¶ИлКҪПөҪyлҠФҙФOУӢ

- dsPICј°ЖдФЪҪ»БчЧғоlХ{ЛЩЦРөД‘ӘУГСРҫҝ

№«ҫW°ІӮд44030402000607

№«ҫW°ІӮд44030402000607