LP62S16256EU-70LLI TTL門的邏輯電平

發布時間:2019/10/25 21:52:53 訪問次數:833

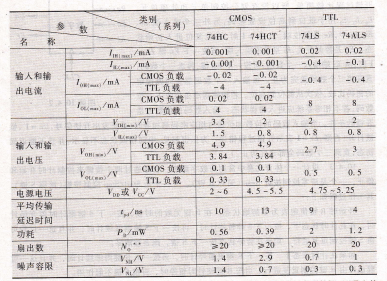

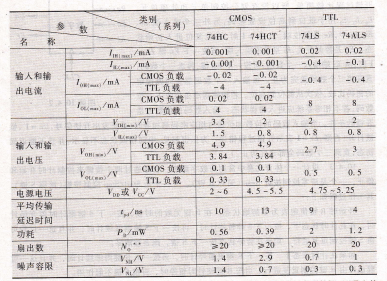

LP62S16256EU-70LLI本附錄的參數參考Texas Instruments公司在可聯網站上提供的集成電路產品數據,以及文獻[3],測量條件為ycc=5Ⅴ,cL=15p「,Td=25℃=74 HC和74HCT的測試頻率為1 MHz.~更詳細的參數、可查閱有關器件的數據手冊。

n0指帶同類門的扇出數,如果保證CMOS驅動門的高電平輸出為4,9V,74HC和74 HCT的n0為20。當允許其高電平輸出降至TTL門的邏輯電平時,Ⅳ。4000,考慮CⅥ0S門的輸人電容的影響,實際要比此數小:

Altera公司的Quartus Ⅱ軟件主要用于開發該公司的FPGA和CPLD器件,它提供邏輯設計、綜合、布局和布線、仿真驗證、對器件編程等功能,可以替代該公司早期的MAX+Plus Ⅱ軟件。目前Quartus Ⅱ 5.0軟件是該公司2005年推出的最新版本。

安裝Quadus Ⅱ 5.0版本的最低硬件配置為:奔騰Ⅱ400 MHz CPU,512 MB以上系統內存,大于1.2 GB安裝該軟件所需的最小硬盤空間。軟件運行環境為: Windows NT4/2000/XP。

利用開發軟件和編程工具對FPGA和CPLD器件進行設計開發的一般設計流程如圖B.1,1所示,它包括設計準各、輸人設計文件、處理設計文件、功能仿真、時序仿真、器件編程和實際測試等步驟。

設計準備,在設計一個數字電路或系統之前,設計者首先根據任務要求,例如系統的功能、復雜度、系統工作速度、成本等因素,選擇合適的設計方案和合適的器件類型,然后采用自頂向下的方法對系統進行劃分,并用適當的方式對系統的邏輯功能進行描述。

LP62S16256EU-70LLI本附錄的參數參考Texas Instruments公司在可聯網站上提供的集成電路產品數據,以及文獻[3],測量條件為ycc=5Ⅴ,cL=15p「,Td=25℃=74 HC和74HCT的測試頻率為1 MHz.~更詳細的參數、可查閱有關器件的數據手冊。

n0指帶同類門的扇出數,如果保證CMOS驅動門的高電平輸出為4,9V,74HC和74 HCT的n0為20。當允許其高電平輸出降至TTL門的邏輯電平時,Ⅳ。4000,考慮CⅥ0S門的輸人電容的影響,實際要比此數小:

Altera公司的Quartus Ⅱ軟件主要用于開發該公司的FPGA和CPLD器件,它提供邏輯設計、綜合、布局和布線、仿真驗證、對器件編程等功能,可以替代該公司早期的MAX+Plus Ⅱ軟件。目前Quartus Ⅱ 5.0軟件是該公司2005年推出的最新版本。

安裝Quadus Ⅱ 5.0版本的最低硬件配置為:奔騰Ⅱ400 MHz CPU,512 MB以上系統內存,大于1.2 GB安裝該軟件所需的最小硬盤空間。軟件運行環境為: Windows NT4/2000/XP。

利用開發軟件和編程工具對FPGA和CPLD器件進行設計開發的一般設計流程如圖B.1,1所示,它包括設計準各、輸人設計文件、處理設計文件、功能仿真、時序仿真、器件編程和實際測試等步驟。

設計準備,在設計一個數字電路或系統之前,設計者首先根據任務要求,例如系統的功能、復雜度、系統工作速度、成本等因素,選擇合適的設計方案和合適的器件類型,然后采用自頂向下的方法對系統進行劃分,并用適當的方式對系統的邏輯功能進行描述。

公網安備44030402000607

公網安備44030402000607