TPS76428DRAM內部的刷新控制及定時電路

發布時間:2020/1/16 12:59:12 訪問次數:1600

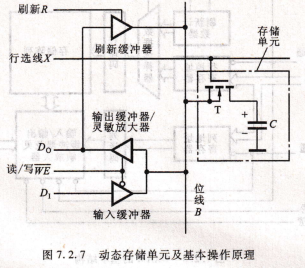

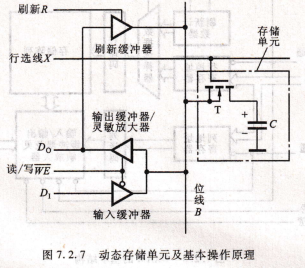

TPS76428讀寫控制WE為高電平,輸出緩沖器/靈敏放大器被選通,C中存儲的數據通過位線和緩沖器輸出(D。再經列選通電路送至最終的輸出引腳)。由于讀出時會消耗C中的電荷,存儲的數據被破壞,故每次讀出后,必須及時對讀出單元刷新,即此時刷新控制R也為高電平,則讀出的數據又經刷新緩沖器和位線對電容器C進行刷新。

刷新R行選線X讀/寫刃百輸入緩沖器,儲元存單位線BDI,隨視存取存儲器動態,存儲單元及基本操作原理,除了讀、寫操作可以對存儲單元進行刷新外,刷新操作也可以通過只選通行選線來實現。例如,當行選線X為高電平,且WE亦為高電平時,C上的數據經T到達位線B,然后經輸入緩沖器對存儲單元刷新,此時的刷新是整行刷新。實際上,輸出緩沖器和刷新緩沖器環路構成一正反饋,如果位線為高電平,則將位線電平拉向更高。反之則使位線電平降得更低。

由于存儲單元電容的容量很小,所以在位線容性負載較大時,C中存儲的電荷(C存有1時)可能還未將位線拉至高電平時便耗盡了,由此出現讀出錯誤。為避免出現這種情況,通常在讀之前先將位線電平預置為高、低電平的中間值。這樣,T導通時,根據電容C存儲的是0還是1,會將位線拉向低電平或高電平。位線電平的這種變化經靈敏放大器放大,可以準確得到C所存儲的邏輯值。

DRAM的基本結構和操作時序,由于DRAM的集成度很高,存儲容量大,因此需要較多的地址線。為減少引線數目,DRAM大都采用行、列地址分時送入的方法。例如,對于一個1M字的存儲器,有22°個地址,即有20根地址線。采用行、列地址分時送人時,只需要10根地址線。DRAM的基本結構如圖7.2.8所示,其內部設有行.

DRAM操作定時圖,(a)讀、寫操作 (b)頁模式讀操作(0E=0) (c)RAs只刷新操作(CAs=7E=1),Cms先于R/4S有效的刷新操作.

執行該操作時,CAs首先變為低電平,然后RAS變為低電平。此時,DRAM內部的刷新控制及定時電路,控制刷新計數器連續生成刷新地址進行刷新操作。

一般的DRAM每行刷新的間隔時間為15.6 us(目前也有7.8 us的),典型的刷新操作時間小于100 ns。刷新時間只占刷新周期的0.64%,所以DRAM用于讀寫操作的時間實際上超過99%。

與SRAM的發展類似,DRAM也有同步DRAM(SDRAM)、雙倍數據傳輸率DRAM(DDR SDRAM)和四倍數據傳輸率DRAM(QDR SDRAM),行地址列地數據輸出,數據輸入行地址存取存儲器.

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

TPS76428讀寫控制WE為高電平,輸出緩沖器/靈敏放大器被選通,C中存儲的數據通過位線和緩沖器輸出(D。再經列選通電路送至最終的輸出引腳)。由于讀出時會消耗C中的電荷,存儲的數據被破壞,故每次讀出后,必須及時對讀出單元刷新,即此時刷新控制R也為高電平,則讀出的數據又經刷新緩沖器和位線對電容器C進行刷新。

刷新R行選線X讀/寫刃百輸入緩沖器,儲元存單位線BDI,隨視存取存儲器動態,存儲單元及基本操作原理,除了讀、寫操作可以對存儲單元進行刷新外,刷新操作也可以通過只選通行選線來實現。例如,當行選線X為高電平,且WE亦為高電平時,C上的數據經T到達位線B,然后經輸入緩沖器對存儲單元刷新,此時的刷新是整行刷新。實際上,輸出緩沖器和刷新緩沖器環路構成一正反饋,如果位線為高電平,則將位線電平拉向更高。反之則使位線電平降得更低。

由于存儲單元電容的容量很小,所以在位線容性負載較大時,C中存儲的電荷(C存有1時)可能還未將位線拉至高電平時便耗盡了,由此出現讀出錯誤。為避免出現這種情況,通常在讀之前先將位線電平預置為高、低電平的中間值。這樣,T導通時,根據電容C存儲的是0還是1,會將位線拉向低電平或高電平。位線電平的這種變化經靈敏放大器放大,可以準確得到C所存儲的邏輯值。

DRAM的基本結構和操作時序,由于DRAM的集成度很高,存儲容量大,因此需要較多的地址線。為減少引線數目,DRAM大都采用行、列地址分時送入的方法。例如,對于一個1M字的存儲器,有22°個地址,即有20根地址線。采用行、列地址分時送人時,只需要10根地址線。DRAM的基本結構如圖7.2.8所示,其內部設有行.

DRAM操作定時圖,(a)讀、寫操作 (b)頁模式讀操作(0E=0) (c)RAs只刷新操作(CAs=7E=1),Cms先于R/4S有效的刷新操作.

執行該操作時,CAs首先變為低電平,然后RAS變為低電平。此時,DRAM內部的刷新控制及定時電路,控制刷新計數器連續生成刷新地址進行刷新操作。

一般的DRAM每行刷新的間隔時間為15.6 us(目前也有7.8 us的),典型的刷新操作時間小于100 ns。刷新時間只占刷新周期的0.64%,所以DRAM用于讀寫操作的時間實際上超過99%。

與SRAM的發展類似,DRAM也有同步DRAM(SDRAM)、雙倍數據傳輸率DRAM(DDR SDRAM)和四倍數據傳輸率DRAM(QDR SDRAM),行地址列地數據輸出,數據輸入行地址存取存儲器.

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

公網安備44030402000607

公網安備44030402000607