TH30081C 外加譯碼器控制存儲器芯片

發布時間:2020/1/16 13:07:04 訪問次數:1771

TH30081C列兩個地址寄存器。行、列地址分別由行地址選通信號RAs①和列地址選通信號CAs②控制,送人各自的寄存器。此外,DRAM內部還設有刷新計數器和刷新控制及定時電路,由此可以自動產生行地址進行刷新。

行地址選通石巒地址月列地址選通C以s數據輸入/輸出J/o讀/寫萬E輸出使能虧刀DRAM的基本結構,DRAM的操作方式比SRAM要復雜些,這里只舉出幾種典型操作。

讀/寫操作,讀/寫操作時,首先RAs和CAS先后變為低電平,將行和列地址分別送入相應地址寄存器。然后在讀寫控制信號WE作用下完成讀/寫操作。讀操作時,輸出使能0E應為低電平。操作時序如圖7.2.3(a)所示。

頁模式操作,所謂“頁”是指同一行的所有列構成的存儲單元。頁模式下的讀寫操作與一般讀寫操作的差別在于不改變行地址,而只改變列地址。但行地址選擇RAS必須始終保持低電平。頁模式可以顯著提高讀寫速度,其讀操作時序如圖7.2.3(b)所示。

RAs只刷新操作,該操作只刷新行地址指定行的所有存儲單元,不進行任何實際的讀寫操作。在整個操作周期CAs要保持高電平,其時序如圖7.2.3(c)所示。該操作一次只刷新一行,且需要外部地址計數器提供刷新地址。

系Row Address strobe的縮寫。

系Column Address strobe的縮寫。

存儲陣列行譯碼,擇器行地址,寄存器列地址,寄存器刷新計,數器刷新控制及定時輸入/輸出,緩沖器及靈敏放大器,存儲器、復雜可編程器件和明場可編程陣列.

由于DRAM的存儲單元結構簡單,其集成度遠高于SRAM,最大容量已達1Gbit,時鐘最高工作頻率達250 MHz。所以同等容量情況下,DRAM更廉價。

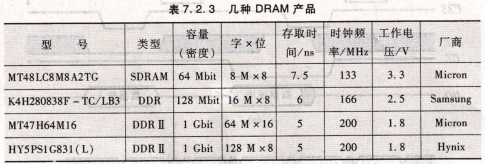

目前,DDR SDRAM已成為個人電腦的主流內存。其改進型DDR ⅡSDRAM將很可能成為下一個主流內存。表7.2.8所示為幾種DRAM產品。

表7.2.3 幾種DRAM產品,MT48LC8M8A2TG,K4H280838F,MT47H64M16,HY5PS1 G831(L).

存儲容量的擴展,目前,盡管各種容量的存儲器產品已經很豐富,且最大容量已達1 Gbit以上,用戶能夠比較方便地選擇所需要的芯片。但是,只用單個芯片不能滿足存儲容量要求的情況仍然存在。個人電腦中的內存條就是一個典型的例子,它由焊在一塊印制電路板上的多個芯片組成。此時,便涉及存儲容量的擴展問題。

擴展存儲容量的方法可以通過增加字長(位數)或字數來實現。

字長(位數)的擴展,通常RAM芯片的字長為1位、4位、8位、16位和32位等。當實際的存儲器系統的字長超過RAM芯片的字長時,需要對RAM實行位擴展。

位擴展可以利用芯片的并聯方式實現,即將RAM的地址線、讀/寫控制線和片選信號對應地并聯在一起,而各個芯片的數據輸人/輸出端作為字的各個位線。如圖7.2.10所示,用4個4K×4位RAM芯片可以擴展成4K×16位的存儲系統。

字數的擴展,字數的擴展可以利用外加譯碼器控制存儲器芯片的片選使能輸人端來實現。例如,利用2線一4線譯碼器74139將4個8K×8位的RAM芯片擴展為32K×8位的存儲器系統。擴展方式如圖7,2,11所示,圖中,存儲器擴展所要增加的地址線我4、A“與譯碼器的74139的輸人相連,譯碼器的輸出‰~y3分別接至4片RAM的片選信號控制端CE。這樣,當輸入一個地址碼(代4~14時,只有一片RAM被選中,從而實現了字的擴展,存儲器、復雜可編程器件和現場可編程門陣列.

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

TH30081C列兩個地址寄存器。行、列地址分別由行地址選通信號RAs①和列地址選通信號CAs②控制,送人各自的寄存器。此外,DRAM內部還設有刷新計數器和刷新控制及定時電路,由此可以自動產生行地址進行刷新。

行地址選通石巒地址月列地址選通C以s數據輸入/輸出J/o讀/寫萬E輸出使能虧刀DRAM的基本結構,DRAM的操作方式比SRAM要復雜些,這里只舉出幾種典型操作。

讀/寫操作,讀/寫操作時,首先RAs和CAS先后變為低電平,將行和列地址分別送入相應地址寄存器。然后在讀寫控制信號WE作用下完成讀/寫操作。讀操作時,輸出使能0E應為低電平。操作時序如圖7.2.3(a)所示。

頁模式操作,所謂“頁”是指同一行的所有列構成的存儲單元。頁模式下的讀寫操作與一般讀寫操作的差別在于不改變行地址,而只改變列地址。但行地址選擇RAS必須始終保持低電平。頁模式可以顯著提高讀寫速度,其讀操作時序如圖7.2.3(b)所示。

RAs只刷新操作,該操作只刷新行地址指定行的所有存儲單元,不進行任何實際的讀寫操作。在整個操作周期CAs要保持高電平,其時序如圖7.2.3(c)所示。該操作一次只刷新一行,且需要外部地址計數器提供刷新地址。

系Row Address strobe的縮寫。

系Column Address strobe的縮寫。

存儲陣列行譯碼,擇器行地址,寄存器列地址,寄存器刷新計,數器刷新控制及定時輸入/輸出,緩沖器及靈敏放大器,存儲器、復雜可編程器件和明場可編程陣列.

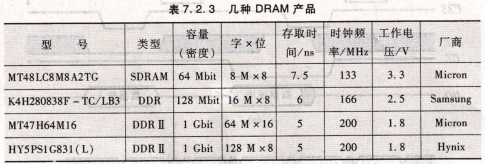

由于DRAM的存儲單元結構簡單,其集成度遠高于SRAM,最大容量已達1Gbit,時鐘最高工作頻率達250 MHz。所以同等容量情況下,DRAM更廉價。

目前,DDR SDRAM已成為個人電腦的主流內存。其改進型DDR ⅡSDRAM將很可能成為下一個主流內存。表7.2.8所示為幾種DRAM產品。

表7.2.3 幾種DRAM產品,MT48LC8M8A2TG,K4H280838F,MT47H64M16,HY5PS1 G831(L).

存儲容量的擴展,目前,盡管各種容量的存儲器產品已經很豐富,且最大容量已達1 Gbit以上,用戶能夠比較方便地選擇所需要的芯片。但是,只用單個芯片不能滿足存儲容量要求的情況仍然存在。個人電腦中的內存條就是一個典型的例子,它由焊在一塊印制電路板上的多個芯片組成。此時,便涉及存儲容量的擴展問題。

擴展存儲容量的方法可以通過增加字長(位數)或字數來實現。

字長(位數)的擴展,通常RAM芯片的字長為1位、4位、8位、16位和32位等。當實際的存儲器系統的字長超過RAM芯片的字長時,需要對RAM實行位擴展。

位擴展可以利用芯片的并聯方式實現,即將RAM的地址線、讀/寫控制線和片選信號對應地并聯在一起,而各個芯片的數據輸人/輸出端作為字的各個位線。如圖7.2.10所示,用4個4K×4位RAM芯片可以擴展成4K×16位的存儲系統。

字數的擴展,字數的擴展可以利用外加譯碼器控制存儲器芯片的片選使能輸人端來實現。例如,利用2線一4線譯碼器74139將4個8K×8位的RAM芯片擴展為32K×8位的存儲器系統。擴展方式如圖7,2,11所示,圖中,存儲器擴展所要增加的地址線我4、A“與譯碼器的74139的輸人相連,譯碼器的輸出‰~y3分別接至4片RAM的片選信號控制端CE。這樣,當輸入一個地址碼(代4~14時,只有一片RAM被選中,從而實現了字的擴展,存儲器、復雜可編程器件和現場可編程門陣列.

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

公網安備44030402000607

公網安備44030402000607