版圖和工藝的考慮

發布時間:2012/4/22 17:09:00 訪問次數:1565

ESD保護電路對幾何尺寸設計是非常敏感的,版圖設計ACT364非常重要。許多ESD保護設計雖然經過模擬有良好的ESD能力,但由于版圖設計不均勻而導致失效。反之,考慮周到的ESD版圖能夠大大改進ESD性能。

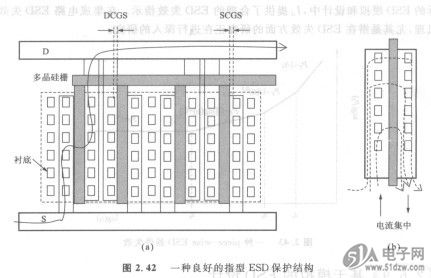

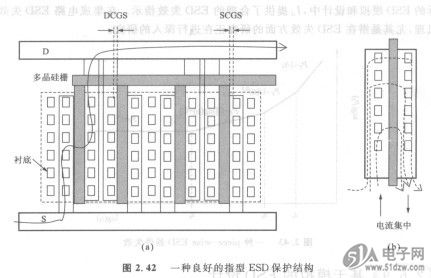

圖2. 42給出了一個優化的多指型ggNMOS結構,它可以得到良好的ESD性能。圖中2. 42(a)的結構保證了單一方向的電流,避免了在圖中(b)存在的電流集中效應。對于電流通路的仔細設計是非常重要的,以避免擁擠而誘發的早期失效(圖2.42(b))。所有器件的角都應該是光滑(圓)的,以避免局部的熱效應。通常在電阻中采用較大的擴散頭,以預防電阻過熱。一些新穎的ESD結構可以允許Pad定向(Pad-oriented)版圖(環繞著PAD)這樣就節省了面積。如果允許的話,應采用盡可能多的接觸孔和通孔。ESD金屬條通常應大于20tlm或盡可能寬。但較 寬的ESD金屬誘導RC寄生效應,對高速、高密度設計帶來不良影響。對于全芯片設計優化來說,電一熱ESD模擬可以用來選擇恰好合適的ESD金屬條寬。從這一點來講,希望包含金屬互連的混合模式ESD模擬器。在NMOS ESD結構中,采用大的漏接觸孔到柵的距離(即drain-contact-to-gate-spacing,DCSG選取大于5肛m,以避免壓艙電阻效應),同時采用較小的源接觸一柵的距離( SCGS),以優化ESD性能。這些規則通常適合于0. 25FLm以上的工藝。但研究表明,最小SCGS規則對于小于0. 25微米技術來說,會導致潛在的ESD失效,這是因為在漏結處產生的熱擴散到源接觸區域,并引起源接觸和金屬的失效。從這一點上講,光誘發過熱是另外一個貢獻因素,在未來的納米級ESD保護設計中將成為一個主要因素。

IC工藝進步對ESD性能可以帶來正面的影響,也可以帶來負面的影響。從負的一方面來講,新技術如LDD、硅化物工藝都使ESD性能嚴重退化。所以需要增加額外的ESD工藝。例如,為了達一目的,普遍增加ESD注入和硅化物阻塞(Sal-icide-blocking)步驟,這樣就增大了工藝開發的費用。從這一角度來講,進行ESD工藝模擬并考慮早期的工藝開發是非常有意義的。從產品開發的角度來講,在ESD性能和器件性能之間折中將有較大的收益。從另外一方面來講,銅互連技術在金屬互連線方面將放寬對ESD的要求。在銅互連工藝中,可以使用窄ESD金屬線,這樣就減少了ESD-金屬誘導的寄生效應,這對于管腳密度較大的芯片設計來講尤其重要。另外一些技術,如SOI和SiGe,在ESD保護設計方面仍然需要更多的研究。

ESD保護電路對幾何尺寸設計是非常敏感的,版圖設計ACT364非常重要。許多ESD保護設計雖然經過模擬有良好的ESD能力,但由于版圖設計不均勻而導致失效。反之,考慮周到的ESD版圖能夠大大改進ESD性能。

圖2. 42給出了一個優化的多指型ggNMOS結構,它可以得到良好的ESD性能。圖中2. 42(a)的結構保證了單一方向的電流,避免了在圖中(b)存在的電流集中效應。對于電流通路的仔細設計是非常重要的,以避免擁擠而誘發的早期失效(圖2.42(b))。所有器件的角都應該是光滑(圓)的,以避免局部的熱效應。通常在電阻中采用較大的擴散頭,以預防電阻過熱。一些新穎的ESD結構可以允許Pad定向(Pad-oriented)版圖(環繞著PAD)這樣就節省了面積。如果允許的話,應采用盡可能多的接觸孔和通孔。ESD金屬條通常應大于20tlm或盡可能寬。但較 寬的ESD金屬誘導RC寄生效應,對高速、高密度設計帶來不良影響。對于全芯片設計優化來說,電一熱ESD模擬可以用來選擇恰好合適的ESD金屬條寬。從這一點來講,希望包含金屬互連的混合模式ESD模擬器。在NMOS ESD結構中,采用大的漏接觸孔到柵的距離(即drain-contact-to-gate-spacing,DCSG選取大于5肛m,以避免壓艙電阻效應),同時采用較小的源接觸一柵的距離( SCGS),以優化ESD性能。這些規則通常適合于0. 25FLm以上的工藝。但研究表明,最小SCGS規則對于小于0. 25微米技術來說,會導致潛在的ESD失效,這是因為在漏結處產生的熱擴散到源接觸區域,并引起源接觸和金屬的失效。從這一點上講,光誘發過熱是另外一個貢獻因素,在未來的納米級ESD保護設計中將成為一個主要因素。

IC工藝進步對ESD性能可以帶來正面的影響,也可以帶來負面的影響。從負的一方面來講,新技術如LDD、硅化物工藝都使ESD性能嚴重退化。所以需要增加額外的ESD工藝。例如,為了達一目的,普遍增加ESD注入和硅化物阻塞(Sal-icide-blocking)步驟,這樣就增大了工藝開發的費用。從這一角度來講,進行ESD工藝模擬并考慮早期的工藝開發是非常有意義的。從產品開發的角度來講,在ESD性能和器件性能之間折中將有較大的收益。從另外一方面來講,銅互連技術在金屬互連線方面將放寬對ESD的要求。在銅互連工藝中,可以使用窄ESD金屬線,這樣就減少了ESD-金屬誘導的寄生效應,這對于管腳密度較大的芯片設計來講尤其重要。另外一些技術,如SOI和SiGe,在ESD保護設計方面仍然需要更多的研究。

公網安備44030402000607

公網安備44030402000607